Article 18

Pour cet article,

consultez également le courrier des lecteurs

Pour cet article,

consultez également le courrier des lecteursComprendre l'électronique par la simulation. par Serge Dusausay Espace lecteur plan du site

Article 18 |

Quelques informations supplémentaires des pages 109 à 114 du livre. |

Pour cet article,

consultez également le courrier des lecteurs Pour cet article,

consultez également le courrier des lecteurs | |

| Les convertisseurs Numérique/Analogique sont des composants primordiaux en électronique, dès lors que l'on travaille avec des circuit logiques et des circuits analogiques. Il était donc indispensable de présenter des résultats expérimentaux qui complètent les simulations présentées dans le livre. |

| ||

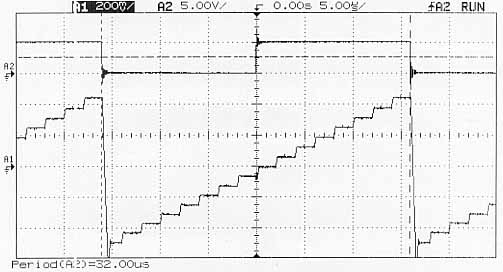

| rampe générée par le compteur + CNA 4 bits | ||

| 5 us / carreau | haut : A2 : 5 V / c | bas : A1 : 200 mV / c |

| ||

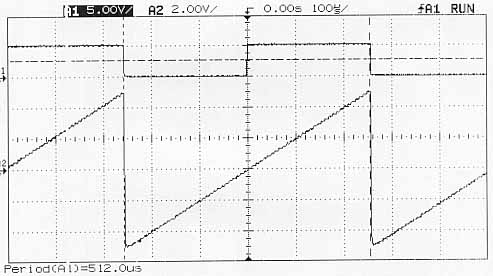

| rampe générée par le compteur + CNA 8 bits | ||

| 100 us / carreau | haut : A1 : 5 V / c | bas : A2 : 2 V / c |

fin de l'article 18

lire le courrier des lecteurs sur cet article