|

les P.D.F. les Papiers Diablement Formateurs

Article 52 :

|

|

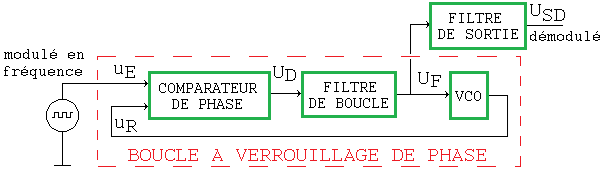

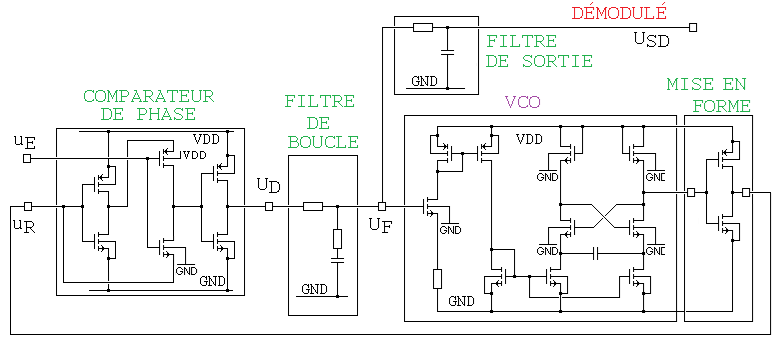

Informations sur cet article : La boucle à verrouillage de phase est un montage complexe. Le schéma qui est proposé comporte au total 20 transistors, ce qui permet de le simuler avec la version d'évaluation de Pspice. Pour faciliter la compréhension, le montage a été découpé en 3 parties, toutes simulées de façon indépendante. Cet article exploite des connaissances d'électronique basiques, et des connaissances d'automatique. L'aspect "mesure" sur une PLL physique n'est pas traité dans cet article, qui est orienté théorie et simulations de vérification. Il est vrai que la manipulation en salle de TP est très riche d'enseignements pour mieux assimiler la théorie. Ce document présente : - le schéma des différents éléments de la PLL, - le fonctionnement de chaque élément, - le fonctionnement de la PLL, utilisée en démodulation de fréquence. Il totalise 12 pages A4 955 kO en format PDF. |

|

Mots clés : système bouclé, asservissement, stabilité, oscillateur, comparateur de phase, filtre, démodulation de fréquence. |

|

Pré requis : automatique linéaire monovariable, fonctions de l'électronique. |

| Pour accéder à la page d'accueil de ce site |

| Pour accéder à des dizaines d'autres PDF sur différents sujets |