|

les P.D.F. les Papiers Diablement Formateurs

Article 49 :

|

|

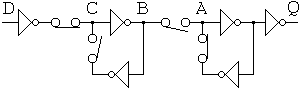

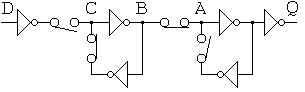

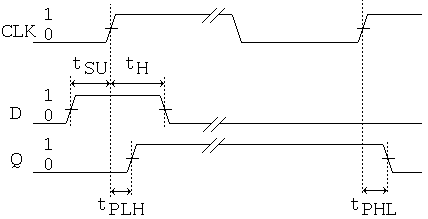

Informations sur cet article : La bascule D flip flop (agissant sur front) est un élément de base de la logique séquentielle. Les constructeurs de ces bascules précisent des temps à respecter pour assurer le bon fonctionnement. Cet article montre, par la simulation analogique, cette notion fine de non respect de temps, appelée violation de temps. Ce document présente : - le schéma de principe d'une bascule D Flip Flop - le schéma réel à transistors - des simulations montrant le fonctionnement - des simulations montrant la violation du temps de set up et du temps de hold - des interprétations Il totalise 3 pages A4 469 kO en format PDF. |

|

Mots clés : transistor en bloqué saturé, fonction interrupteur. temps de setup, temps de hold |

|

Pré requis : transistor MOS |

| Pour accéder à la page d'accueil de ce site |

| Pour accéder à des dizaines d'autres PDF sur différents sujets |