Comprendre l'électronique par la simulation. par Serge Dusausay Espace lecteur plan du site

Article 13 |

Quelques informations supplémentaires des pages 85 à 90 du livre. |

|

Dans cette page, on se propose de comparer simulation/pratique du circuit

amplificateur à base de 2N3819. Le montage est câblé conformément au schéma de la page 86 du livre, à l'exception de la résistance série de 100 kOhm qui a été volontairement omise, jusqu'au paragraphe 3.b. |

| ||

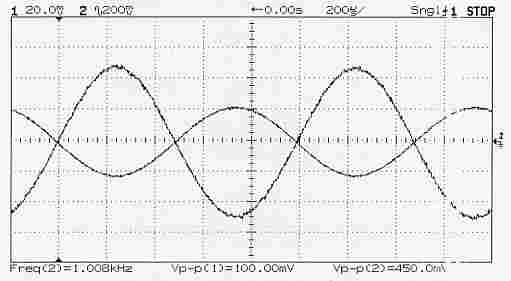

| Fonctionnement de l'amplificateur source commune | ||

| 200 us / carreau | CH1 : 20 m V / c | CH2 : 200 mV / c AC |

| ||

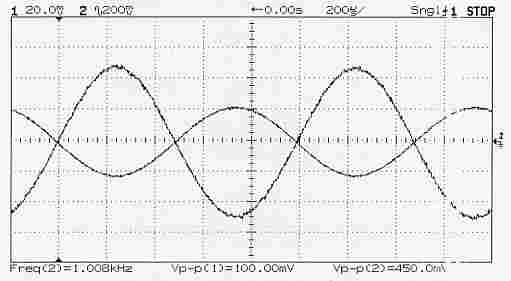

| mêmes traces, en XY | ||

| CH1 : 50 m V / c | CH2 : 500 mV / c AC | |

| ||

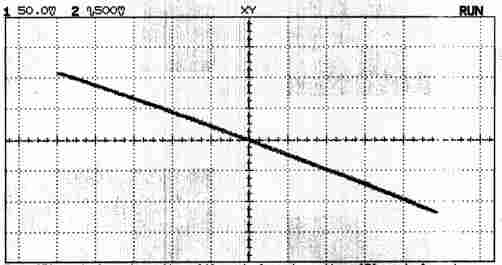

| amplificateur en haut niveau : distorsion | ||

| 200 us / carreau | haut : CH1 : 1 V / c | bas : CH2 : 2 V / c AC |

| ||

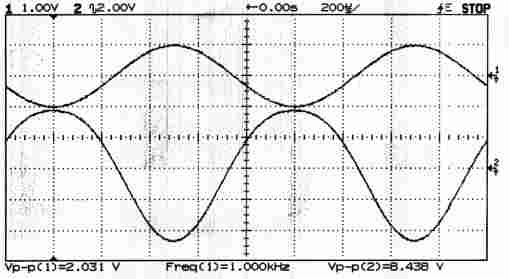

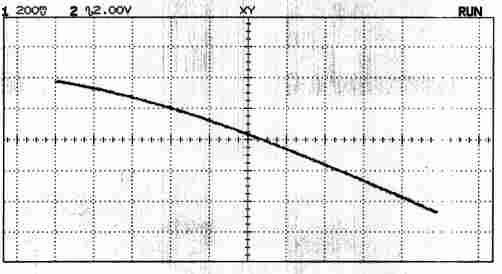

| mêmes traces, en XY | ||

| CH1 : 200 m V / c | CH2 : 2 V / c AC | |

Il est important de signaler qu'une mesure directe de VGS est à proscrire :

Il est important de signaler qu'une mesure directe de VGS est à proscrire :

|

fin de l'article 13