Comprendre l'électronique par la simulation. par Serge Dusausay Espace lecteur plan du site

Article 05 |

Quelques informations supplémentaires des pages 41 à 44 du livre. |

|

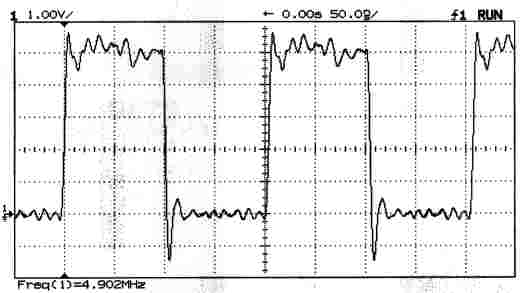

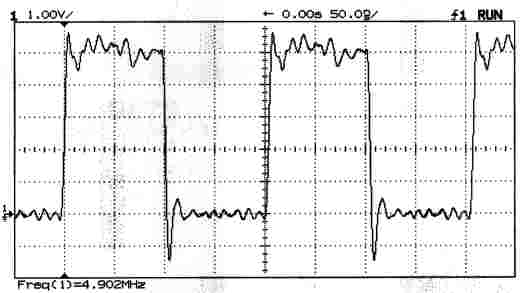

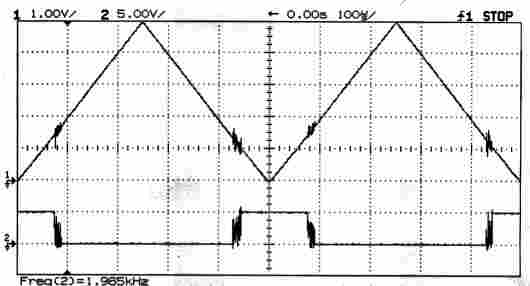

Le livre montre comment déterminer le temps de traversée d'un inverseur logique : il suffit de réaliser un oscillateur en anneau à l'aide d'une chaîne d'inverseurs rebouclée (page 43). Est présentée ci-dessous le résultat d'une manipulation similaire à celle montrée dans le livre. |

| ||

| Oscillateur en anneau, 17 inverseurs CMOS 74 HCT 04 | ||

| 50 ns / carreau | CH1 : 1 V / c | |

| ||

| Réponse expérimentale | ||

| 100 us / carreau | haut : CH1 : 1 V / c | bas : CH2 : 5 V / c |

fin de l'article 05