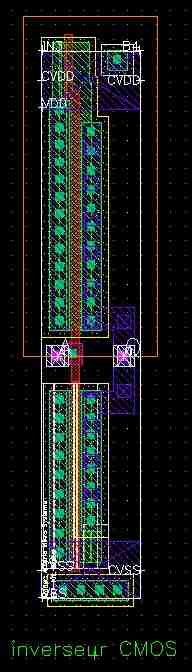

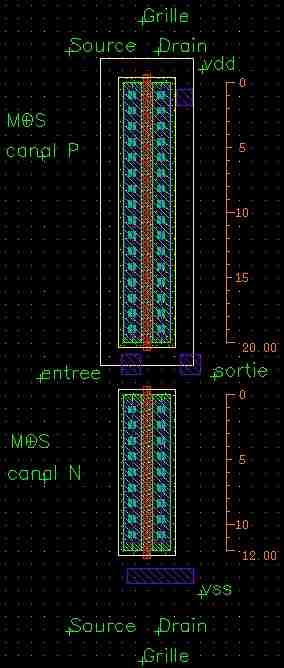

un transistor MOS canal P, un transistor MOS canal N

pour voir cette image, en meilleure résolution (73 kO), mais sur une nouvelle fenêtre, cliquer.

- en haut, la succession bleu, rouge, bleu, dans le rectangle vert inscrit dans le rectangle blanc signifie :

Un caisson P, avec à l'intérieur Source, Grille, Drain d'un transistor canal P.

La largeur est de 20 um.

La longeur est de 0,6 um.

- en bas, la succession bleu, rouge, bleu, dans le rectangle vert signifie :

Source, Grille, Drain d'un transistor canal N.

La largeur est de 12 um.

La longeur est de 0,6 um.