article 100

# Un amplificateur à transistors JFET et bipolaires

J'invite le lecteur à consulter le site pour des informations complémentaires.

Page d'accueil du site Internet : page d'accueil

d'autres pdf, sur différents sujets : <mark>liste des PDF</mark>

Cet article, à but pédagogique, montre l'association d'un JFET en « source commune » d'un PNP en « base commune », et d'un NPN en « collecteur commun »...

La cascade de ces 3 montages fondamentaux donne un amplificateur moyennes fréquences, dont nous allons caractériser le fonctionnement.

La source est: <a href="https://www.next.gr/rf/amplifiers/Broadcast-band-rf-amplifier-l13377.html">https://www.next.gr/rf/amplifiers/Broadcast-band-rf-amplifier-l13377.html</a>

Sous ce site, quelques lignes d'explication sont données, ainsi que les caractéristiques de la réponse harmonique : gain 30 dB, bande en fréquence [100 Hz; 3 MHz]. Le texte indique que la « sortie RF » peut débiter sur 50  $\Omega$ . Pas d'information numérique sur la polarisation, ni sur le fonctionnement temporel (tension maximale de sortie ?). Et aucun calcul, ni simulation, ni essais pratiques...

C'est donc un schéma intéressant, mais qui mérite d'être analysé plus finement.

Mes premières simulations sur ce schéma m'ont montré que les caractéristiques données n'étaient pas obtenues, surtout avec une charge de  $50 \Omega$  en sortie.

J'ai dû modifier les valeurs numériques de quelques résistances pour disposer d'un ampli plus performant que je présente ici. Par la suite, un nouveau schéma, amélioré, est proposé.

# 1) Analyse théorique du schéma.

## 1.a) Présentation succincte

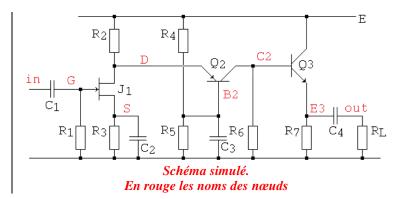

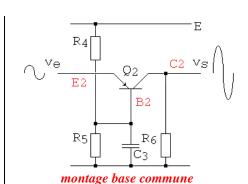

L'entrée est sur le JFET  $J_1$ , monté en source commune, découplage par  $C_2$ . La sortie de cet étage est sur l'émetteur de  $Q_2$ , monté en base commune, découplage par  $C_3$ . On ajoute  $Q_3$ , étage collecteur commun pour pouvoir débiter sur une faible impédance.

Les transistors sont en liaison directe.  $C_1$  et  $C_4$  sont des condensateurs de liaison qui coupent les composantes continues, pour ne pas perturber la polarisation.

L'amplificateur est inverseur, par l'étage  $J_1$ . La résistance  $R_3$  permet de régler sa polarisation. Les étages à  $Q_2$  et  $Q_3$  sont non inverseurs.

Le JFET est un MPF102. Il est ancien (obsolète), d'usage général, et est dans la librairie JFET.lib

Les transistors bipolaires sont : 2N3906 ( $f_T = 250$  MHz à  $I_C = 10$  mA) et 2N3904 ( $f_T = 300$  MHz à  $I_C = 10$  mA). Ils sont dans eval.lib.

## 1.b) Calcul de la polarisation

#### - Etage J<sub>1</sub>.

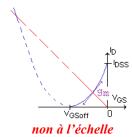

Remarque: La data sheet du MPF102 indique I<sub>DSS</sub> entre 2 mA et 20 mA, et V<sub>GSoff</sub> à – 8 V max.

Les valeurs typiques de ces paramètres ne sont pas données par le constructeur.

Pour un calcul de la polarisation, on peut exploiter les valeurs numériques données par le modèle PSpice.

Sous Pspice: V<sub>GSoff</sub> est nommé VTO, et vaut -3,41 V.

$$I_{DSS} = \beta \text{ VTO}^2$$

.  $\beta \text{ vaut } 1,04 \ 10^{-3}$ . Il en résulte  $I_{DSS} = 1,04 \ 10^{-3}$  x  $3,41^2 = 12,09$  mA.

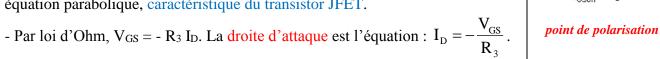

La maille d'entrée donne un système de 2 équations à 2 inconnues :

- En première approximation, en régime saturé :  $I_D = I_{DSS} (1 - \frac{V_{GS}}{V_{GSoff}})^2$ ,

équation parabolique, caractéristique du transistor JFET.

La valeur de R<sub>3</sub> permet le réglage du courant de polarisation du JFET. Si R<sub>3</sub> diminue, la pente de la droite d'attaque augmente et  $|V_{GS}|$  diminue,  $I_D$  augmente. (A l'extrême, si  $R_3 = 0$ ,  $V_{GS} = 0$ ,  $I_D = I_{DSS}$ ).

Le point de fonctionnement peut se lire sur le plan I<sub>D</sub>, V<sub>GS</sub>, ou par le calcul.

L'annexe 1 donne le calcul. Pour

$$R_3 = 180 \Omega$$

, on obtient  $I_D = 5.8 \text{ mA}$  et  $V_{GS} = -1.046 \text{ V}$ .

#### - Etage Q<sub>2</sub>.

On admet I<sub>B2</sub> négligeable devant le courant de pont R<sub>4</sub> R<sub>5</sub>.

D'où

$$V_{B2} = E R_5 / (R_4 + R_5) = 12 \times 3.3 \text{ k} / (1.8 \text{ k} + 3.3 \text{ k}) = 7.765 \text{ V}.$$

On admet  $V_{EB2} \approx 0.7 \text{ V}$ . Il vient :  $V_D \approx 7.765 + 0.7 = 8.465 \text{ V}$ .

$R_2$  est soumise à  $(E - V_D) = 12 - 8,465 = 3,535V$ , et donc parcourue par  $I_{R2} = 3,535 / 560 = 6,3$  mA.

Comme

$$I_{C2} = I_{E2}$$

, la loi des nœuds donne  $I_{C2} = I_{R2} - I_{D1} = 6.3 \text{ mA} - 5.8 \text{ mA}$ .  $I_{C2} = 0.5 \text{ mA}$ .

Devant cette valeur, l'hypothèse I<sub>C2</sub> >> I<sub>B3</sub> n'est probablement pas vérifiée.

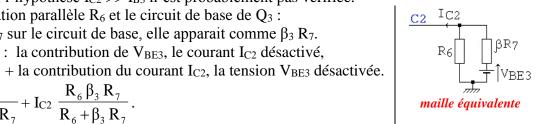

Observons l'association parallèle R<sub>6</sub> et le circuit de base de Q<sub>3</sub> :

En faisant glisser  $R_7$  sur le circuit de base, elle apparait comme  $\beta_3$   $R_7$ .

Le potentiel  $V_{C2}$  est : la contribution de  $V_{BE3}$ , le courant  $I_{C2}$  désactivé,

$$Soit: V_{BE3} \; \frac{R_{_{6}}}{R_{_{6}}+\beta_{_{3}}\,R_{_{7}}} + I_{C2} \; \frac{R_{_{6}}\,\beta_{_{3}}\,R_{_{7}}}{R_{_{6}}+\beta_{_{3}}\,R_{_{7}}} \, .$$

On admet

$$V_{BE3} = 0.76 \text{ V}$$

et  $\beta_3 = 165$  (valeurs confirmées par la suite). Il vient  $V_{C2} = 0.76 \ \frac{15 \ k}{15 \ k + 165 \ x \, 150} + 0.5 \ m \ \frac{15 \ k}{15 \ k + 165 \ x \, 150} = 0.287 + 4.669. \ \boxed{V_{C2} = 4.96 \ V}.$

#### - Etage Q<sub>3</sub>.

$$V_{E3} = V_{C2} - V_{BE3} = 4,96 - 0,76 = 4,2 \text{ V}.$$

Le transistor sera polarisé avec  $I_{E3} = V_{E3} / R_7$ , soit 4,2 / 150.  $I_{E3} = 28 \text{ mA}$ .

Remarque : la dynamique du potentiel de V<sub>E3</sub> n'est pas [0; E], mais dépend de celle de V<sub>C2</sub>. Et le potentiel de V<sub>C2</sub> est lié à R<sub>6</sub> et I<sub>C2</sub>, lui-même dépendant de R<sub>2</sub> et I<sub>D</sub>, donc de R<sub>3</sub>...

Au bilan, R<sub>3</sub> règle la polarisation de J<sub>1</sub>, mais, par loi des nœuds au potentiel D, également celle de Q<sub>2</sub>, conjointement avec le pont R<sub>4</sub>, R<sub>5</sub>, puis, par le choix de R<sub>6</sub> et R<sub>7</sub>, celle de Q<sub>3</sub>.

Il est bon de rappeler que les paramètres I<sub>DSS</sub> et V<sub>GSoff</sub> du JFET sont donnés avec une très large tolérance. La polarisation calculée et/ou simulée peut donc être très différente de celle obtenue en pratique. Ce genre de montage, peu robuste, nécessite des résistances réglables pour ajuster la polarisation.

Q2N3906

# 1.c) Simulation de la polarisation (annexe 4 fichier ampli\_j\_2bip.cir)

La simulation .OP de Pspice confirme, pour les 3 transistors, les courants calculés.

On repère, pour le paragraphe suivant :  $g_{m1} = 4,97 \ 10^{-3}$ .  $g_{m2} = 0,0189$ .  $g_{m3} = 144$ .  $g_{m3} = 0,833$ .

|          | ITB                                                                                               | -Z.38E-U6                                      | 1.66E-U4                                                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | IC                                                                                                | -4.93E-04                                      | 2.74E-02                                                                                                                                                            |

| T1       | VBE                                                                                               | -6.84E-01                                      | 7.59E-01                                                                                                                                                            |

|          | VBC                                                                                               | 2.87E+00                                       | -7.10E+00                                                                                                                                                           |

|          | VCE                                                                                               | -3.55E+00                                      | 7.86E+00                                                                                                                                                            |

|          | BETADC                                                                                            | 2.07E+02                                       | 1.65E+02                                                                                                                                                            |

|          | GM                                                                                                | 1.89E-02                                       | 8.33E-01                                                                                                                                                            |

|          | RPI                                                                                               | 1.09E+04                                       | 1.73E+02                                                                                                                                                            |

|          | RX                                                                                                | 1.00E+01                                       | 1.00E+01                                                                                                                                                            |

|          | RO                                                                                                | 4.38E+04                                       | 2.96E+03                                                                                                                                                            |

|          | CBE                                                                                               | 1.70E-11                                       | 2.61E-10                                                                                                                                                            |

| 7.05E-15 | CBC                                                                                               | 3.92E-12                                       | 1.76E-12                                                                                                                                                            |

|          | CJS                                                                                               | 0.00E+00                                       | 0.00E+00                                                                                                                                                            |

|          | BETAAC                                                                                            | 2.06E+02                                       | 1.44E+02                                                                                                                                                            |

|          | J1<br>MPF102<br>5.84E-03<br>-1.05E+00<br>7.40E+00<br>4.97E-03<br>1.15E-05<br>1.86E-12<br>7.09E-13 | IC VBE VBC | IC -4.93E-04 VBE -6.84E-01 WPF102 VBC 2.87E+00 5.84E-03 VCE -3.55E+00 BETADC 2.07E+02 4.97E-03 RPI 1.09E+04 1.15E-05 RX 1.00E+01 1.86E-12 CBC 3.92E-12 CJS 0.00E+00 |

MODEL

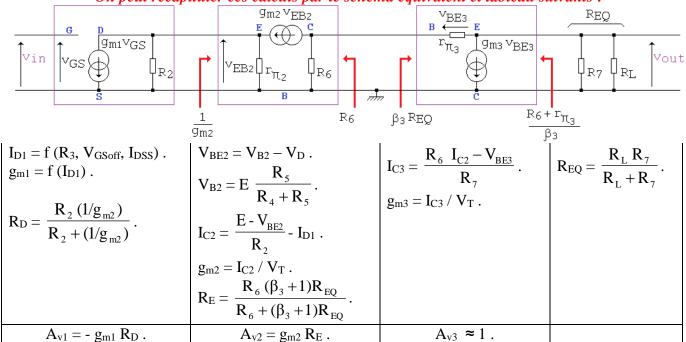

## 2) Réponse harmonique : amplification petits signaux

## 2.a) Prédétermination des amplifications en tension de chaque étage

Le montage base commune intrinsèque dispose d'une impédance d'entrée =  $1/g_{m2} = 52,91 \Omega$ .

Cette faible valeur pénalise l'amplification en tension du source commune. En effet, posons  $R_D$ , l'association parallèle de cette impédance avec  $R_2$ .  $R_D = 52,91~\Omega$  //  $560~\Omega = 48,34~\Omega$ .

L'étage source commune a une amplification en tension  $A_{v1} = -g_{m1} R_D$ , soit 4,97  $10^{-3}$  x  $48,34 = \boxed{-0,24}$ . Remarque : l'annexe 2 montre que l'on peut prédéterminer la valeur de  $g_{m1}$ .

L'émetteur suiveur débite sur  $R_L = 50 \Omega$  en parallèle avec  $R_7$ .

Posons  $R_{EO} = R_L // R_7 = 50 \Omega // 150 \Omega = 37.5 \Omega$ .

Son impédance d'entrée est ( $\beta_3+1$ )  $R_{EO}=145$  x 37.5=5.437 k $\Omega$ , en négligeant  $r_{\pi 3}$ .

Posons R<sub>E</sub>, l'association R<sub>6</sub> avec cette impédance : R<sub>E</sub> = 15 k $\Omega$  // 5,437 k $\Omega$  = 3,99 k $\Omega$ .

L'étage base commune a une amplification en tension  $A_{v2} = g_{m2} R_E$ , (en négligeant la présence de  $r_0$ ), soit  $0.0189 \times 3.99 \text{ k} = \boxed{75.42}$ .

Ce collecteur commun a une amplification

$$A_{v3} = \frac{g_{m3} R_{EQ}}{1 + g_{m3} R_{EQ}} = \frac{0.833 \times 37.5}{1 + 0.833 \times 37.5} = \boxed{0.97}.$$

Son impédance de sortie est  $(R_6 + r_{\pi 3}) / \beta_3 = (15 \text{ k} + 173) / 144 = 105,4 \Omega.$

En milieu de bande, on attend une amplification totale de  $A_{v1}$   $A_{v2}$   $A_{v3} = -0.24$  x 75,42 x 0,97 = -17,54.

article 100

#### **Commentaires:**

Lisons le tableau de droite à gauche :

A  $R_L$  imposée (50  $\Omega$ ),  $R_{EO}$  est fonction de  $R_7$ .

A<sub>v3</sub> est fonction de R<sub>EO</sub> et de g<sub>m3</sub>.

g<sub>m3</sub> est fonction de I<sub>C3</sub>, lui-même fonction de I<sub>C2</sub>.

$A_{v2}$  est fonction de  $g_{m2}$ , elle-même fonction de  $I_{C2}$ , et de  $R_E$ , fonction de  $R_6$  et  $R_{EQ}$ .

I<sub>C2</sub> est fonction du pont diviseur de tension R<sub>5</sub>, R<sub>4</sub>, du potentiel V<sub>D</sub> et de I<sub>D1</sub>.

$A_{v1}$  est fonction de  $g_{m1}$ , elle-même fonction de  $I_{D1}$  qui dépend de  $R_3$ , et de  $R_D$ , fonction de  $R_2$  et  $g_{m2}$ .

Il est clair que les 3 étages ne sont pas indépendants.

$\rightarrow$  en petits signaux, pour avoir une amplification en tension maximale, il ne faut pas chercher à maximiser chaque étage : la recherche d'avoir  $A_{v1} > 1$  a conséquence de diminuer fortement  $A_{v2}$ .

$\rightarrow$  en grands signaux : pour avoir la dynamique de tension maximale en sortie (et donc d'une puissance maximale dans  $R_L$ ), on est amené à choisir un point de polarisation du collecteur commun à fort courant, (donc  $R_7$  faible), ce qui diminue  $R_{EQ}$  et donc  $R_E$  et donc  $A_{v2}$ ...

Et si l'inégalité  $g_{m3}$   $R_{EQ} >> 1$  n'est plus respectée, on a une chute de  $A_{v3}$ .

## 2.b) Simulation de l'amplification petits signaux.

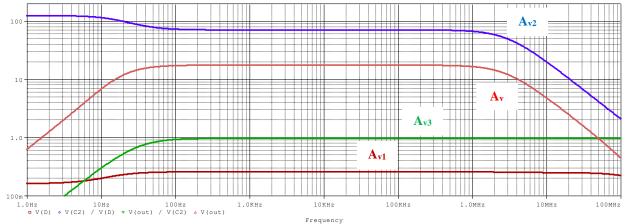

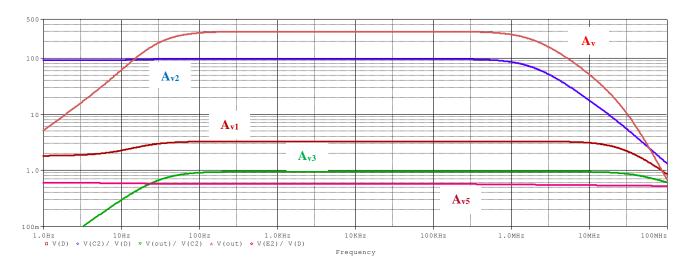

Réponse harmonique de chaque étage. Echelle log en ordonnées

#### **Interprétation:**

Les ordonnées sont en échelle log, et affichent directement l'amplification de chaque étage.

En milieu de bande, à 10 kHz, on retrouve les amplifications en tension attendues :

L'étage  $J_1$ : 0,257 (0,24 prédéterminé), l'étage  $Q_2$ : 70,4 (75,4 prédéterminé) et l'étage  $Q_3$ : 0,967 (0,97 prédéterminé).

L'amplification totale est 17,5 (17,54 prédéterminé).

Les coupures basses sont liées aux condensateurs  $C_1$  à  $C_4$ , les coupures hautes aux condensateurs internes aux transistors. C'est le JFET qui pénalise les hautes fréquences.

| Cutoff_Lowpass_3dB(V(out))  | 2.85113meg   |

|-----------------------------|--------------|

| Cutoff_Highpass_3dB(V(out)) | 21.68753     |

| Bande passante: [21 Hz;     | ; 2,85 MHz ] |

L'intérêt du montage en base commune est qu'il n'y a pas de condensateurs de jonction ( $C_{BE}$  ou  $C_{BC}$ ) entre l'entrée et la sortie d'un étage amplificateur de tension. Donc pas d'effet Miller.

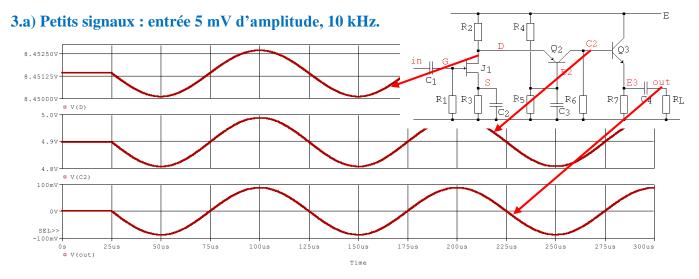

## 3) Réponse temporelle : amplification petits et grands signaux, milieu de bande.

## **Interprétation:**

Le signal d'entrée est appliqué à  $t = 25 \mu s$ . Cela permet de lire facilement les potentiels de polarisation.

Le potentiel de Drain est porté par une composante continue de 8,45 V, ce que donnait la polarisation.

| 1   |          |          |          |          |

|-----|----------|----------|----------|----------|

|     | X Values | 200.000u | 250.000u | -50.000u |

| ſ   | V(D)     | 8.4527   | 8.4501   | 2.5721m  |

| - T |          |          |          |          |

En plaçant les curseurs sur les valeurs crête (séparées par une demi période, soit 50  $\mu$ s), on peut mesurer l'amplification :  $A_{v1} = 2,5721 \text{ mV} / 10 \text{ mV} = 0,257$  (en opposition de phase avec l'entrée).

De même, pour le potentiel  $C_2$ . Polarisation 4,894 V, et 180 mV càc, soit  $A_{v1}$  x  $A_{v2}$  = - 18, d'où  $A_{v2}$  = 69,9.

|   | X Values | 200.000u | 250.000u | -50.000u |

|---|----------|----------|----------|----------|

|   | V(C2)    | 4.9871   | 4.8073   | 179.854m |

| _ | 1        |          |          |          |

|   |          |          |          |          |

| 1 | X Values | 200.000u | 250.000u | -50.000u |

La sortie du montage complet présente un signal de 174  $\,$  mV càc, soit  $A_v = 17,4$  (en opposition de phase avec l'entrée).

On retrouve bien sûr les valeurs établies en réponse harmonique, car on travaille en petits signaux, et les équations qui gèrent le circuit apparaissent comme linéaires.

Remarque : en affichant le graphe 17.5\*V(in) on obtient un sinusoïde qui se superpose à V(out).

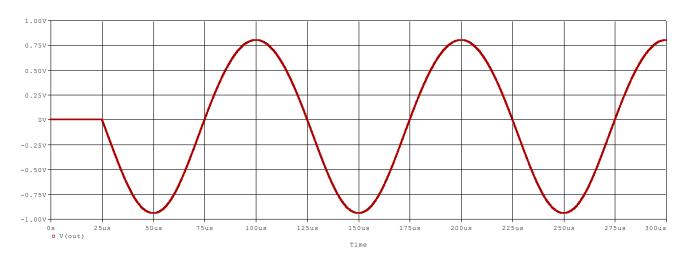

## 3.b) Grands signaux, entrée 50 mV d'amplitude, 10 kHz.

## **Interprétation:**

Avec une amplitude de 50 mV en entrée, soit 100 mV càc, on a, en sortie V(out) une sinusoïde qui présente une légère distorsion et qui délivre 1,744 V càc, soit une amplification en tension apparente de 17,44.

article 100

En conclusion, ce montage présente, pour une amplitude d'entrée inférieure à 50 mV environ, une amplification en tension de - 17,5, soit une amplitude maximale en sortie de 0,87 V sur  $50 \Omega$  avant distorsion. La bande passante est [21 Hz; 2,85 MHz].

L'étude théorique et les simulations montrent 2 défauts évidents : l'étage d'entrée qui n'amplifie pas la tension, mais qui atténue, et l'étage de sortie qui présente une impédance d'entrée qui pénalise l'amplification du deuxième étage, et sa polarisation. Ce schéma peut être amélioré.

## 4) Pistes d'améliorations

On respecte l'esprit du schéma d'origine, notamment en utilisant les mêmes transistors. On exploite la série E24 pour les résistances, sauf pour R<sub>5</sub>.

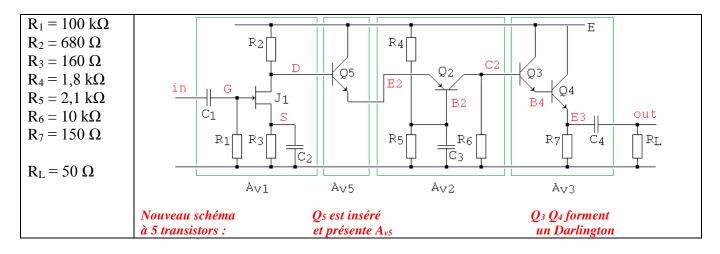

#### 4.a) Les modifications du schéma

## - on intercale un émetteur suiveur entre l'étage 1 et l'étage 2.

De ce fait, l'impédance ramenée par Q<sub>2</sub> est beaucoup plus grande, et A<sub>v1</sub> augmente.

#### - on place un Darlington sur l'étage de sortie, afin que $Q_3$ soit à « super $\beta$ ».

La conséquence directe est un courant de base (polarisation et dynamique)  $\beta$  fois plus faible, et donc de moins perturber l'étage  $Q_2$ , ce qui fait augmenter  $A_{v2}$ . On réalise le Darlington avec un autre 2N 3904.

Cela nécessite de modifier les valeurs numériques des résistances, afin de réajuster la polarisation.

On conserve la nomination  $J_1$ ,  $Q_2$ ,  $Q_3$  d'origine.

On appelle Q<sub>5</sub> le transistor connecté à J<sub>1</sub> et on appelle Q<sub>4</sub>, l'associé à Q<sub>3</sub>, qui forme le Darlington.

On conserve les termes A<sub>v1</sub>, A<sub>v2</sub>, A<sub>v3</sub> précédents.

## **4.a)** Polarisation (annexe 5 fichier ampli\_j\_4bip.cir)

La polarisation de  $J_1$  fixe le potentiel de D, et, par conséquence, celui de  $E_2$ , séparé de  $V_{BE5}$ . Pour éviter de faire rentrer  $Q_2$  en saturation, il faut avoir |VCE2| > |VCEsat|, c'est à dire le potentiel  $C_2$  suffisamment faible, ce qui est contradictoire avec une large dynamique de tension en  $E_3$ , d'où en V(out). Le schéma présenté est le fruit de plusieurs essais de valeurs numériques des résistances. Il a été privilégié ici de maximiser l'amplification en tension et non la dynamique de sortie.

|       |           | NAME   | <b>Q</b> 5 | Q2        | Q3        | Q4        |

|-------|-----------|--------|------------|-----------|-----------|-----------|

|       |           | MODEL  | Q2N3904    | Q2N3906   | Q2N3904   | Q2N3904   |

|       |           | IB     | 4.52E-06   | -3.17E-06 | 1.62E-06  | 1.83E-04  |

|       |           | IC     | 5.87E-04   | -5.88E-04 | 1.82E-04  | 2.97E-02  |

|       |           | VBE    | 6.50E-01   | -6.91E-01 | 6.19E-01  | 7.61E-01  |

|       |           | VBC    | -4.19E+00  | 6.02E-01  | -6.14E+00 | -6.76E+00 |

| 1     |           | VCE    | 4.84E+00   | -1.29E+00 | 6.76E+00  | 7.52E+00  |

| NAME  | J1        | BETADC | 1.30E+02   | 1.85E+02  | 1.12E+02  | 1.62E+02  |

| MODEL | MPF102    | GM     | 2.25E-02   | 2.25E-02  | 7.00E-03  | 8.90E-01  |

| ID    | 6.16E-03  | RPI    | 6.69E+03   | 8.15E+03  | 1.88E+04  | 1.57E+02  |

| VGS   | -9.86E-01 | RX     | 1.00E+01   | 1.00E+01  | 1.00E+01  | 1.00E+01  |

| VDS   | 6.82E+00  | RO     | 1.33E+05   | 3.28E+04  | 4.42E+05  | 2.72E+03  |

| GM    | 5.10E-03  | CBE    | 1.32E-11   | 1.77E-11  | 8.39E-12  | 2.79E-10  |

| GDS   | 1.22E-05  | CBC    | 2.03E-12   | 6.93E-12  | 1.84E-12  | 1.79E-12  |

| CGS   | 1.88E-12  | CJS    | 0.00E+00   | 0.00E+00  | 0.00E+00  | 0.00E+00  |

| CGD   | 7.28E-13  | BETAAC | 1.50E+02   | 1.84E+02  | 1.32E+02  | 1.40E+02  |

On remarque que VCE2 n'est que de 1,29 V.

#### 4.c) Analyse harmonique, bande passante

On peut reprendre le schéma donné en page 3.

- L'insertion de Q<sub>5</sub> permet d'isoler l'étage J<sub>1</sub> de Q<sub>2</sub>.

Néanmoins Q<sub>5</sub> ramène sur le Drain de J<sub>1</sub> une impédance  $\beta_5$  x  $1/g_{m2} = 150$  x 1/0,0225 = 6,6 k $\Omega$

On pose R'<sub>D</sub> =

$$\frac{R_2 (\beta_5/g_{m2})}{R_2 + (\beta_5/g_{m2})} = \frac{680 \text{ x } 6.6\text{k}}{680 + 6.6\text{k}} = 616 \Omega.$$

L'amplification  $A_{v1}$  est alors  $-g_{m1} R'_{D} = -5.1 \cdot 10^{-3} \times 616 \text{ soit } A_{v1} = -3.14$

- Comme vu précédemment, l'étage  $Q_2$  présente une impédance d'entrée  $1/g_{m2}$ .

Il s'ensuit que  $A_{v5}$ , amplification de l'étage  $Q_5$ , en est :  $\frac{g_{m5} \ 1/g_{m2}}{1+g_{m5} \ 1/g_{m2}} \ .$

Le courant continu qui passe dans Q<sub>5</sub> passe également dans Q<sub>2</sub>

Comme  $g_m = I_C / V_T$ , nous aurons  $g_{m2} = g_{m5}$  d'où, par conséquence,  $A_{v5} = 0.5$

On peut remarquer que l'amélioration créée par  $Q_5$  est entachée d'une atténuation de 2.

La présence de r<sub>0</sub> ne peut pas être négligée. L'annexe 3 donne le calcul de l'amplification en tension de la base commune.

- L'étage central fournit donc

$$A_{v2} = R_6 \left( \frac{g_m + \frac{1}{r_0}}{1 + \frac{R_6}{r_0}} \right), \text{ soit } 10 \text{ k} \left( \frac{0,0225}{1 + \frac{1}{32,8 \text{ k}}} \right) : \boxed{A_{v2} = 172,7}.$$

- L'insertion de Q<sub>4</sub> améliore l'impédance d'entrée de l'étage de sortie. On conserve  $A_{v3} = 1$ .

L'amplification en tension attendue est  $A_{v1}$  x  $A_{v5}$  x  $A_{v2}$  x  $A_{v3}$ .

Soit respectivement :  $A_v = -3.14 \times 0.5 \times 172.7 \times 1 = -271.1$ .

#### La simulation AC confirme ces calculs:

## **Interprétation:**

| 10.000K  |

|----------|

| 3.2768   |

| 170.959  |

| 943.721m |

| 298.245  |

| 564.142m |

|          |

| Calculé:        |

|-----------------|

| $A_{v1} = 3,14$ |

| $A_{v2} = 172,$ |

| $A_{v3} = 1$    |

| $A_v = 272,7$   |

| $A_{v5} = 0.5$  |

En milieu de bande, les amplifications de chaque étage simulées sont en accord avec les calculs de prédétermination.

→ Ce montage présente une amplification en tension de près de 300, soit 49,5 dB.

La bande passante est sensiblement inchangée par rapport à la version 3 transistors.

#### Remarque:

on peut améliorer la fréquence de coupure basse : en fixant  $C_4$  à 1000  $\mu F$  (au lieu de 100  $\mu F$  ), elle passe à 13,9 Hz.

| Cutoff_Low  | pass_3dB(V(out)) | 1.89530meg |

|-------------|------------------|------------|

| Cutoff_High | pass_3dB(V(out)) | 36.49155   |

Bande passante : [ 36 Hz ; 1,9 MHz ]

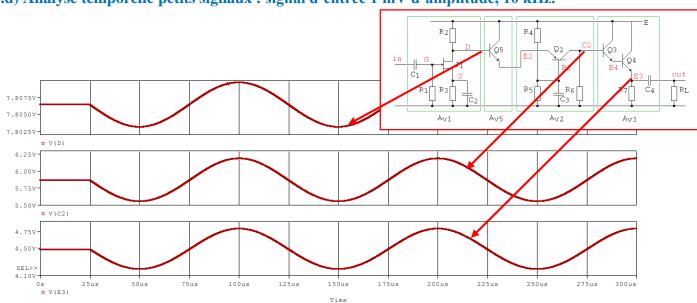

## 4.d) Analyse temporelle petits signaux : signal d'entrée 1 mV d'amplitude, 10 kHz.

#### **Interprétation:**

Avec une amplification attendue de 300, il faut injecter un très faible signal à l'entrée pour qu'on reste en régime linéaire en sortie. Il a été choisi une amplitude de 1 mV, donc 2 mV càc. Le signal d'entrée est appliqué à t = 25 µs. On lit ainsi les potentiels de polarisation.

article 100

- Le potentiel de Drain est polarisé à 7,8064 V. Une sinusoïde se superpose avec une variation crête à crête de 6,55 mV, en opposition de phase. On déduit  $A_{v1}$ = 3,275.

- En C2, le potentiel continu est 5,8629 V. La variation càc est 631,7 mV, soit  $A_{v5}$  x  $A_{v2}$  = 631,7 / 6,55 = 96,44

- En E3, le potentiel continu est 4,4822 V. La variation est de 596 mV. Le Darlington a donc  $A_{v3}=596/631,7=0,94$ .

| X Values | 200.000u | 250.000u | -50.000u |

|----------|----------|----------|----------|

| V(E3)    | 4.7880   | 4.1923   | 595.733m |

| V(C2)    | 6.1853   | 5.5537   | 631.662m |

| V(D)     | 7.8097   | 7.8031   | 6.5494m  |

2 curseurs permettent de mesurer les variations crête à crête.

Comme nous sommes en petits signaux, les valeurs issues de ce run sont en parfaite cohérence avec le run AC. Observons maintenant entrée et sortie de tout le montage :

#### **Interprétation:**

L'amplification en tension globale se lit facilement : 2 mV càc en entrée, 600 mV càc en sortie, en opposition de phase :  $A_v = -300$ .

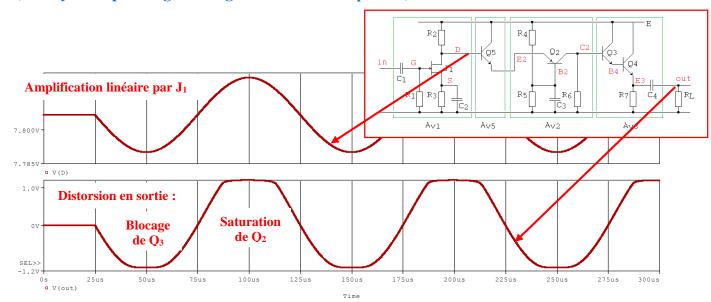

#### 4.e) Analyse temporelle grands signaux : 5 mV d'amplitude, 10 kHz.

#### **Interprétation:**

En injectant une sinusoïde de 5 mV d'amplitude, l'étage d'entrée ne présente pas de distorsion. Il fournit en D une sinusoïde de 32,9 mV càc, ce qui reste dans le domaine petits signaux devant la dynamique de tension possible en D.

Avec 10 mV càc en entrée, on déduit une amplification de 3,29 : on retrouve la valeur de A<sub>v1</sub>.

Par contre, une nette déformation se présente en sortie du montage complet. Celle-ci s'explique pour 2 raisons :

- Le blocage de  $Q_3$ ,  $V_{BE3}$  descend sous 500 mV, visualisable par V(C2) V(B4),

- Saturation de  $Q_2$ ,  $V_{CE2}$  atteint 60 mV, visualisable par V(C2) V(E2).

La déformation du signal de sortie se manifeste quand l'amplitude de l'entrée dépasse 3 mV, soit environ 0,9 V en sortie.

En conclusion, ce montage présente, pour une amplitude d'entrée inférieure à 3 mV environ, une amplification en tension de - 300, soit une amplitude maximale en sortie de 0,9 V sur  $50 \Omega$  avant distorsion. La bande passante est [ 36 Hz ; 1,9 MHz ].

## **Conclusion**

A partir d'un schéma trouvé sur le Net, cet article a présenté une synthèse, sur un seul montage, de plusieurs connaissances de l'électronique analogique. Les simulations ont confirmé les calculs faits « à la main ».

Le schéma d'origine est simple, mais les inconvénients cités le rendent peu intéressant. Le passage à la version à 5 transistors est une vraie évolution, et il forme un bel exemple pédagogique de différents chapitres de l'électronique analogique.

Remarquons néanmoins qu'il n'y a pas un aspect industriel dans cette étude :

Les valeurs des paramètres  $I_{DSS}$ ,  $V_{GSoff}$  du JFET n'étant pas garanties, un changement de composant peut nécessiter de modifier la polarisation.

De plus, il n'a pas été étudié la robustesse vis à vis de la tension d'alimentation. Par exemple, un écart de cette dernière modifie – faiblement – le courant circulant dans R<sub>2</sub>, ce qui a néanmoins pour conséquence de modifier les courants de polarisation des 4 transistors bipolaires. Et par la suite, l'amplification en tension.

On pourrait également analyser la conséquence d'un changement de température, qui agit sur les courants de repos, et donc sur l'amplification...

## Annexe 1

## Point de polarisation

D'où: a = 0.00104 $\Delta = 10,965 \ 10^{-5}$

Résolution de :

$$I_{DSS}(1 - \frac{V_{GS}}{V_{GSoff}})^2 = -\frac{V_{GS}}{R_3}$$

article 100

En développant et ordonnant, on obtient le trinôme :

$$V_{GS}^2 \frac{I_{DSS}}{V_{GSoff}^2} + V_{GS} \left(\frac{1}{R_3} - 2 \frac{I_{DSS}}{V_{GSoff}}\right) + I_{DSS} = 0. \quad \text{Que l'on peut écrire simplement : a $v^2 + b$ $v + c = 0$.}$$

On pose classiquement :  $\Delta = b^2 - 4$  a c. Les racines sont donc :  $\frac{-b \pm \sqrt{\Delta}}{2 a}$ .

$V_{GSoff} = -3.41 \text{ V}$   $R_3 = 180 \Omega$ . A. N. :  $I_{DSS} = 12,09 \text{ mA}$ ,

$$\begin{array}{ll} b = 0.0126 & c = 0.01209 \\ \text{solution}: \boxed{V_{GS} = -1.046 \text{ V}} & \text{d'où } \boxed{I_D = 5.8 \text{ mA}} \end{array}$$

(l'autre solution est éliminée : correspond à l'autre intersection, placée en pointillé ci-contre)

#### Annexe 2

Calcul de  $g_m$ , pente de la caractéristique  $I_D = f(V_{GS})$ , au point de polarisation :

$$g_{\rm m} = \frac{dI_{\rm D}}{dV_{\rm GS}} = -2\frac{I_{\rm DSS}}{V_{\rm GSoff}}(1 - \frac{V_{\rm GS}}{V_{\rm GSoff}}) , \ soit \ -2\frac{12,09\ m}{-3,41}(1 - \frac{\text{--}1,046}{\text{--}3,41}) = \boxed{4,916\ m\Omega^{\text{--}1}}.$$

Remarque : il est très fréquent d'avoir la valeur numérique de  $g_m$  (en  $\Omega^{-1}$ ) proche de celle de  $I_D$  (en A).

Remarque : Comme illustré sur le graphe, pour bénéficier d'une valeur élevée à gm, il est préférable de travaille à I<sub>D</sub> proche de I<sub>DSS</sub>, c'est à dire |V<sub>GS</sub>| proche de 0 V. Par contre, cela réduit la dynamique de tension applicable à l'entrée.

## Annexe 3:

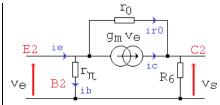

amplification en tension du montage base commune en tenant compte de  $r_0$ .

schéma équivalent en dynamique,

La polarisation assure, à chaque électrode, un potentiel continu.

Autour des potentiels continus en E2 et C2, des signaux variables sont présents, respectivement ve, vs, pour signifier entrée et sortie de cet étage.

Le modèle du transistor est classiquement une source de courant i<sub>c</sub> commandée par une tension v<sub>eb</sub>, soit ici,  $i_c = g_m v_e$ , car la base est au 0 V dynamique.

Pour modéliser l'imperfection de la source de courant émetteur - collecteur, la résistance r<sub>0</sub> est ajoutée.

$v_s = R_6 \; (i_c + i_{r0}) \qquad \quad o\grave{u} \qquad \; i_c = g_m \; v_e \label{eq:vs}$

$$\begin{split} v_s &= R_6 \; (i_c + i_{r0}) \qquad \text{où} \qquad i_c = g_m \; v_e \qquad \quad et \qquad i_{r0} = (v_e - v_s) \, / \, r_0 \\ v_s &= R_6 \; g_m \; v_e + R_6 \; \frac{v_e}{r_o} - R_6 \; \frac{v_s}{r_o} \; \; \text{soit} : \qquad \quad v_s \; (1 + \frac{R_6}{r_o}) = \; v_e \; R_6 \; (g_m + \frac{1}{r_o}) \end{split}$$

La tension v<sub>s</sub> s'écrit : En développant, on a :

$\text{Il vient alors}: \left| \frac{v_s}{v_e} = R_6 \frac{g_m + \frac{1}{r_0}}{1 + \frac{R_6}{r_0}} \right|. \qquad \qquad \text{Remarque}: \text{si } r_0 \to \infty, \ \frac{v_s}{v_e} \text{ tend vers } g_m \ R_6.$

# Annexe 4 : fichier. ampli\_j\_2bip.cir, prêt à simuler

article 100

| Amplificateur à 3 transistors       | Q2 C2 B2 D Q2N3906 ; PNP C B E |

|-------------------------------------|--------------------------------|

| * fichier ampli j 2bip.cir          | R4 A B2 1.8k                   |

| * circuit                           | C3 B2 0 10uF                   |

| .LIB eval.lib                       | R5 B2 0 3.3k                   |

| .LIB JFET.lib                       | R6 C2 0 15k                    |

|                                     | Q3 A C2 E3 Q2N3904 ; NPN C B E |

| VCC A 0 DC=12                       | R7 E3 0 150                    |

| Vin in 0 sin(0 5m 10k 25u 0 0) AC=1 | C4 E3 out 100uF                |

| C1 in G 10uF                        | RL out 0 50                    |

| R1 G 0 100k                         | .OP                            |

| J1 D G S MPF102 ; D G S             | .AC DEC 100 1 100MEG           |

|                                     | .TRAN 10ns 300us 0 10ns        |

| R2 A D 560                          | .probe                         |

| R3 S 0 180                          | . END                          |

| C2 S 0 100uF                        |                                |

# Annexe 5 : fichier. ampli\_j\_4bip.cir, prêt à simuler

| Amplificateur à 5 transistors       | Q2 C2 B2 E2 Q2N3906 ; PNP C B E |  |

|-------------------------------------|---------------------------------|--|

| * fichier ampli_j_4bip.cir          | R4 A B2 1.8k                    |  |

| * circuit                           | R5 B2 0 2.1k                    |  |

| .LIB eval.lib                       | C3 B2 0 10uF                    |  |

| .LIB JFET.lib                       | R6 C2 0 10k                     |  |

|                                     | Q3 A C2 B4 Q2N3904 ; NPN C B E  |  |

| Valim A 0 DC=12                     | Q4 A B4 E3 Q2N3904 ; NPN C B E  |  |

| Vin in 0 sin(0 1m 10k 25u 0 0) AC=1 | R7 E3 0 150                     |  |

| C1 in G 10uF                        | C4 E3 out 100uF                 |  |

| R1 G 0 100k                         | RL out 0 50                     |  |

| J1 D G S MPF102 ; D G S             | .OP                             |  |

| R2 A D 680                          | .AC DEC 100 1 100MEG            |  |

| R3 S 0 160                          | .TRAN 10ns 300u 0 10ns          |  |

| C2 S 0 100uF                        | .probe                          |  |

| Q5 A D E2 Q2N3904 ; NPN C B E       | . END                           |  |

# articles 1 à 43 : sur le livre

|    | Tableau récapitulatif des articles PDF disponibles sur ce site |                     |                     |  |  |  |

|----|----------------------------------------------------------------|---------------------|---------------------|--|--|--|

| n° | titre                                                          | lien présentation   | lien direct article |  |  |  |

|    | Guide d'installation et d'emploi simplifié                     | présentation        | document PDF        |  |  |  |

| 44 | Exemples basiques et des exercices                             | présentation        | document PDF        |  |  |  |

| 45 | Un exemple de circuit passif                                   | présentation        | document PDF        |  |  |  |

| 46 | Un oscillateur Colpitts                                        | présentation        | document PDF        |  |  |  |

| 47 | Compensation en fréquence des amplificateurs opérationnels     | présentation        | document PDF        |  |  |  |

| 48 | Un amplificateur à transistors bipolaires                      | présentation        | document PDF        |  |  |  |

| 49 | Une bascule D Flip Flop CMOS                                   | présentation        | document PDF        |  |  |  |

| 50 | Une porte XOR à transistors MOS                                | présentation        | document PDF        |  |  |  |

| 51 | Un VCO à 12 transistors MOS                                    | présentation        | document PDF        |  |  |  |

| 52 | Une PLL à moins de 20 transistors MOS                          | présentation        | document PDF        |  |  |  |

| 53 | Un oscillateur à résistance négative                           | présentation        | document PDF        |  |  |  |

| 54 | Une charge électronique                                        | <u>présentation</u> | document PDF        |  |  |  |

| 55 | Un amplificateur en classe C                                   | présentation        | document PDF        |  |  |  |

| 56 | Le monostable 74 123                                           | présentation        | document PDF        |  |  |  |

| 57 | Un amplificateur en classe D                                   | présentation        | document PDF        |  |  |  |

| 58 | Le transformateur en linéaire                                  | présentation        | document PDF        |  |  |  |

| 59 | La loi d'ohm thermique                                         | présentation        | document PDF        |  |  |  |

| 60 | Le transformateur en non linéaire                              | présentation        | document PDF        |  |  |  |

| 61 | Robustesse d'un oscillateur en anneau                          | présentation        | document PDF        |  |  |  |

| 62 | Une alimentation stabilisée                                    | présentation        | document PDF        |  |  |  |

| 63 | Modélisation d'un haut-parleur                                 | présentation        | document PDF        |  |  |  |

| 64 | Un synthétiseur de fréquence                                   | présentation        | document PDF        |  |  |  |

| 65 | Un ampli audio de Sparkfun                                     | présentation        | document PDF        |  |  |  |

| 66 | Simulation logique et analogique                               | présentation        | document PDF        |  |  |  |

| 67 | Un oscillateur à relaxation                                    | présentation        | document PDF        |  |  |  |

| 68 | Lecteur de TAG RFID 125 kHz                                    | présentation        | document PDF        |  |  |  |

| 69 | Diagramme de l'œil avec Pspice                                 | présentation        | document PDF        |  |  |  |

| 70 | Un amplificateur hautes fréquences                             | présentation        | document PDF        |  |  |  |

| 71 | Une bizarrerie enfin expliquée                                 | présentation        | document PDF        |  |  |  |

| 72 | Comprendre le paramétrage de la FFT                            | présentation        | document PDF        |  |  |  |

| 73 | La relation de Bennett                                         | présentation        | document PDF        |  |  |  |

| 74 | Simuler un circuit à plus de 20 transistors avec PSpice Eval   | présentation        | document PDF        |  |  |  |

| 75 | Une horloge biphase sans recouvrement                          | présentation        | document PDF        |  |  |  |

| 76 | Quelques simulations sur la diode                              | présentation        | document PDF        |  |  |  |

| 77 | Un ampli classe A, avec transformateur de sortie               | présentation        | document PDF        |  |  |  |

| 78 | Des stimuli pour PSpice                                        | présentation        | document PDF        |  |  |  |

| 79 | Simuler le TL431 : zener ajustable                             | présentation        | document PDF        |  |  |  |

| 80 | Un ADC flash                                                   | présentation        | document PDF        |  |  |  |

| 81 | Une chaine d'acquisition : S&H, ADC, DAC                       | présentation        | document PDF        |  |  |  |

| 82 | Un amplificateur 50 MHz                                        | présentation        | document PDF        |  |  |  |

| 83 | Un dérivateur non inverseur                                    | présentation        | document PDF        |  |  |  |

| 84 | Un amplificateur bipolaire avec push pull CMOS                 | présentation        | document PDF        |  |  |  |

| 85 | Rôle des répéteurs logiques dans un circuit intégré            | présentation        | document PDF        |  |  |  |

| 86 | Un driver logique CMOS pour charge 50 ohms                     | présentation        | document PDF        |  |  |  |

| 87 | Des triggers de Schmitt et des applications                    | présentation        | document PDF        |  |  |  |

| 88 | Un filtre gaussien analogique                                  | présentation        | document PDF        |  |  |  |

| 89 | Un générateur de bruit rose                                    | <u>présentation</u> | document PDF        |  |  |  |

|    | on generation de bruit 1000                                    | E                   |                     |  |  |  |

| Comprendre l'électronique par la simulation, par S. Dusausay article 100                          |                                                            | pages supplémen     | taires 2024/2025 |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|------------------|

| 90                                                                                                | Un anémomètre à fil chaud : simulation comportementale     | <u>présentation</u> | document PDF     |

| 91                                                                                                | Un oscillateur à pont de Wien stabilisé par CTN            | <u>présentation</u> | document PDF     |

| 92                                                                                                | L'emballement thermique d'une diode                        | <u>présentation</u> | document PDF     |

| 93                                                                                                | Les puissances dans un amplificateur                       | <u>présentation</u> | document PDF     |

| 94                                                                                                | Asservissement de puissance dans une résistance            | <u>présentation</u> | document PDF     |

| 95                                                                                                | Asservissement de la puissance émise par une antenne radio | <u>présentation</u> | document PDF     |

| 96                                                                                                | Un driver de LED de puissance                              | <u>présentation</u> | document PDF     |

| 97                                                                                                | Exploiter Pspice pour simuler des filtres numériques       | <u>présentation</u> | document PDF     |

| 98                                                                                                | Un filtre en cosinus surélevé avec Pspice                  | <u>présentation</u> | document PDF     |

| 99                                                                                                | Effet de la température sur un amplificateur en classe A   | <u>présentation</u> | document PDF     |

| 100                                                                                               | Un amplificateur à transistors JFET et bipolaires          | <u>présentation</u> | document PDF     |

|                                                                                                   |                                                            |                     |                  |

|                                                                                                   |                                                            |                     |                  |

|                                                                                                   |                                                            |                     |                  |

|                                                                                                   |                                                            |                     |                  |

|                                                                                                   |                                                            |                     |                  |

|                                                                                                   |                                                            |                     |                  |

| Supplément, hors article :                                                                        |                                                            |                     |                  |

| mon cours « Electronique pour les communications numériques ». polycopié couleur 201 pages en pdf |                                                            |                     |                  |

retour à l'écran d'accueil de ce site