#### un ADC flash 3 bit

article 80

J'invite le lecteur à consulter le site pour des informations complémentaires.

Page d'accueil du site Internet : page d'accueil

d'autres pdf, sur différents sujets : liste des PDF

Parmi les différents procédés pour réaliser la conversion Analogique / Numérique, il existe la structure « flash », ou « parallèle » ou « directe ». Le principe de cette conversion est simple, d'où un schéma —de principe- avec peu de composants, ce qui permet des simulations avec Pspice d'évaluation. On montre ici le fonctionnement d'un ADC 3 bits.

## 1) L'ADC (ou CAN) flash

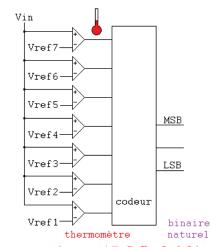

### 1.a) Schéma de principe

La tension à convertir est comparée à N seuils de tension, à l'aide de N comparateurs tout ou rien. La sortie de ces N comparateurs donne une information binaire, appelée code thermomètre, liée à la tension d'entrée (si la tension monte, l'indication monte).

Un codeur transforme le code thermomètre en code binaire naturel.

Pour un ADC n bits, il faut  $N = 2^n - 1$  comparateurs : ici, N = 7 comparateurs, pour un ADC 3 bits.

Le convertisseur ADC flash 3 bits

Il est facile de comprendre que des hautes résolutions sont difficiles à obtenir : 8 bits nécessitent 255 comparateurs, et 255 références de tension distinctes.

#### 1.b) Structure

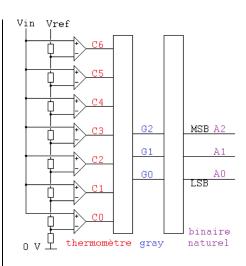

Ici, par simplicité, les N tensions de référence sont fabriquées à partir d'un pont diviseur de tension alimenté par une tension de référence unique, externe.

Nous allons travailler avec des comparateurs identiques, parfaits (pas de courant entrant, pas de tension de mode commun...).

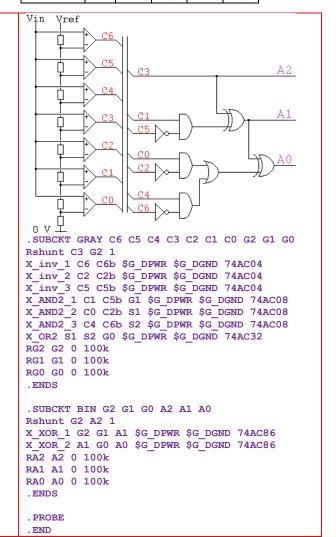

Il a été choisi un codeur formé de 2 parties : un passage du code thermomètre au code de Gray, puis un passage du code de Gray au code binaire naturel.

Les 7 seuils de tension sont positifs, par conséquence, Vin est positif également.

On choisit une alimentation unique de 5 V pour toute l'électronique.

Le convertisseur ADC flash 3 bits

#### 1.c) Comment faire un comparateur

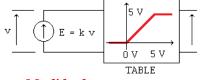

Idéalement, un comparateur tout ou rien doit disposer d'une amplification en tension infinie, et sa sortie ne peut prendre que 2 valeurs possibles : état haut et état bas.

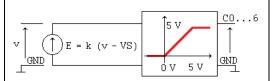

article 80

La façon choisie ici est de faire appel à un **modèle** de comparateur, grâce à une source de tension commandée par une tension, avec un écrêtage de la tension de sortie. Sous Pspice, ceci peut être obtenu très simplement par la source E, affectée d'une fonction tabulée. Le coefficient d'amplification k a été choisi arbitrairement à 500. Pour être compatible avec la logique qui lui est connectée, l'état bas est 0 V, l'état haut 5 V.

Modèle de comparateur tout ou rien

Remarquons que le défaut de ce modèle est le risque d'avoir une tension en sortie à une valeur intermédiaire entre 0 V et 5 V : cela arrive si v est proche de 0, c'est à dire e+ proche de e-.

## 1.d) Le transcodeur thermomètre / Gray / binaire naturel

Observons la table de vérité:

|                     |           | code thermomètre |           |           |           |           |           | cod | e de G | Fray | binaire   |           |           |

|---------------------|-----------|------------------|-----------|-----------|-----------|-----------|-----------|-----|--------|------|-----------|-----------|-----------|

| Vin                 | <b>C6</b> | <b>C5</b>        | <b>C4</b> | <b>C3</b> | <b>C2</b> | <b>C1</b> | <b>C0</b> | G2  | G1     | G0   | <b>A2</b> | <b>A1</b> | <b>A0</b> |

| Vin < Vref1         | 0         | 0                | 0         | 0         | 0         | 0         | 0         | 0   | 0      | 0    | 0         | 0         | 0         |

| Vref1 < Vin < Vref2 | 0         | 0                | 0         | 0         | 0         | 0         | 1         | 0   | 0      | 1    | 0         | 0         | 1         |

| Vref2 < Vin < Vref3 | 0         | 0                | 0         | 0         | 0         | 1         | 1         | 0   | 1      | 1    | 0         | 1         | 0         |

| Vref3 < Vin < Vref4 | 0         | 0                | 0         | 0         | 1         | 1         | 1         | 0   | 1      | 0    | 0         | 1         | 1         |

| Vref4 < Vin < Vref5 | 0         | 0                | 0         | 1         | 1         | 1         | 1         | 1   | 1      | 0    | 1         | 0         | 0         |

| Vref5 < Vin < Vref6 | 0         | 0                | 1         | 1         | 1         | 1         | 1         | 1   | 1      | 1    | 1         | 0         | 1         |

| Vref6 < Vin < Vref7 | 0         | 1                | 1         | 1         | 1         | 1         | 1         | 1   | 0      | 1    | 1         | 1         | 0         |

| Vref7 < Vin         | 1         | 1                | 1         | 1         | 1         | 1         | 1         | 1   | 0      | 0    | 1         | 1         | 1         |

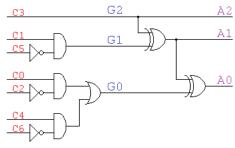

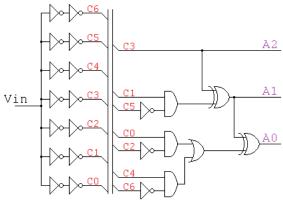

L'annexe 1 donne les tableaux de Karnaugh qui permettent de déduire les équations :

$$G2 = C3$$

$$G1 = C1\overline{C5}$$

$$G0 = C0\overline{C2} + C4\overline{C6}$$

A2 = G2

A1 = G2 XOR G1

A0 = G2 XOR G1 XOR G0 = A1 XOR G0

Le schéma résultant est donné ci-contre :

schéma du transcodeur

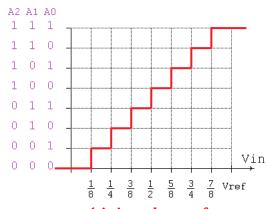

## 1.e) Caractéristique de transfert statique théorique

La table de vérité peut également se présenter par la courbe valeur binaire = f (tension d'entrée).

Le quantum est Vref/8, soit, pour Vref = 5 V, q = 0.625 V.

Si Vin >  $\frac{7}{8}$  Vref, la valeur binaire reste bloquée à 111, et si

Vin < Vref/8, la valeur binaire reste bloquée à 000.

La pleine échelle (full scale) est Vref – 1  $q = \frac{7}{8}$  Vref.

caractéristique de transfert

## 2) Simulation de l'ADC flash (netlist en annexe 2) fichier ADC 3b.cir

#### 2.a) Choix du signal d'entrée

On choisit une référence à 5 V. Avec 8 résistances identiques ( $10 \text{ k}\Omega$ , arbitrairement) pour le pont diviseur de tension, les 7 seuils seront : 0.625 V ; 1.25 V ; 1.875 V ; 2.5 V ; 3.125 V ; 3.75 V ; 4.375 V. Une façon simple de tester le convertisseur, est de placer une tension d'entrée qui couvre toute la dynamique. Une loi en rampe est adaptée pour suivre aisément les 3 bits de sortie qui suivent le code binaire naturel. Cela justifie un signal de dynamique 0 V à 5 V.

## 2.b) Choix de la technologie pour la logique du décodeur

Il a été choisi la famille 74AC, disponible dans les librairies de Pspice. C'est une ancienne technologie CMOS, conçue pour être alimentée de 2 V à 6 V. On exploite ainsi les 74AC04 (inverseur), 74AC08 (ET à 2 entrées), 74AC32 (OU à 2 entrées), 74AC86 (OU exclusif à 2 entrées). Remarquons que l'électronique interne (à base de transistors MOS) n'est pas simulée : c'est un modèle fonctionnel qui est exploité par Pspice. En consultant la librairie 74AC.lib, ainsi que dig\_io.lib, on peut lire que les portes sont définies par des sous-circuits, dans lesquels on dispose :

- de la fonction logique à proprement parler,

- des paramètres statiques (niveau 0 = potentiel de DGND = 0 V, niveau 1 = potentiel de DPWR = 5 V)

- de l'interface avec un éventuel environnement analogique (AtoD et DtoA, entre autres)

- des paramètres dynamiques (par exemple les délais d'un inverseur : tp<sub>LH</sub> = 4 ns et tp<sub>HL</sub> = 3,5 ns) Cela offre un degré de réalisme (cohérence avec les circuits vrais) suffisant pour nos simulations de notre convertisseur, qui, rappelons-le, est analysé globalement sur le plan comportemental.

#### 2.c) Vérification du fonctionnement

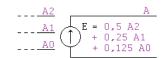

En plus de la visualisation des sorties des décodeurs, on peut visualiser la valeur <u>analogique</u> correspondant au code binaire A2, A1, A0. Pour ce faire, on ajoute un convertisseur Numérique / Analogique parfait. Ce convertisseur additif est tout simplement une source de tension commandée par 3 tensions :

Une source E réalise un convertisseur N / A parfait

On exploite que les niveaux haut et bas des sorties de la 74AC sont 5 V et 0 V pour reconstruire, à partir d'un sommateur pondéré, la tension analogique. On affecte en A2 le coefficient 0,5, en A1 le coefficient 0,25 et en A0 le coefficient 0,125 : on dispose ainsi d'une tension en A allant de 0 V à 4,375 V.

L'affichage des signaux logiques montre des booléens. Mais il est plus pratique de visualiser des signaux dans un « plot » analogique. Pour ce faire on doit connecter sur les sorties logiques un environnement analogique. Cela justifie les résistances de charge de  $100~\mathrm{k}\Omega$  (valeur arbitraire) afin d'accéder à des niveaux  $0~\mathrm{V}$  5 V et non des valeurs binaires  $0~\mathrm{et}$  1.

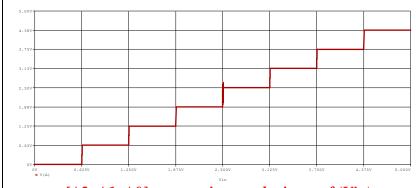

#### 2.d) Essai en statique

Par une directive .DC, on balaie toute la tension de façon continument variable, en statique.

Grâce à l'artifice du CNA parfait qui a été ajouté, on peut lire, sous forme tension =  $A2 \times 0.5 + A1 \times 0.25 + A0 \times 0.125$  l'information binaire de sortie A2, A2, A0.

On retrouve la caractéristique de transfert statique.

[A2, A1, A0], converti en analogique = f(Vin)

On peut néanmoins remarquer un petit défaut lors de la transition  $011 \rightarrow 100$ , lié à la combinaison de A2 qui présente un potentiel qui augmente alors que A1, A0 diminuent.

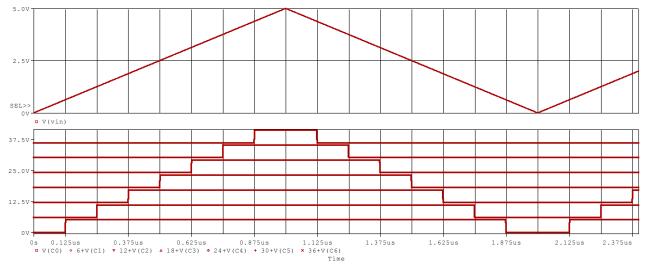

# 2.e) Essai en dynamique

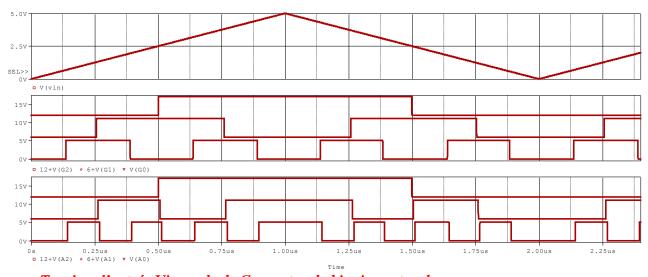

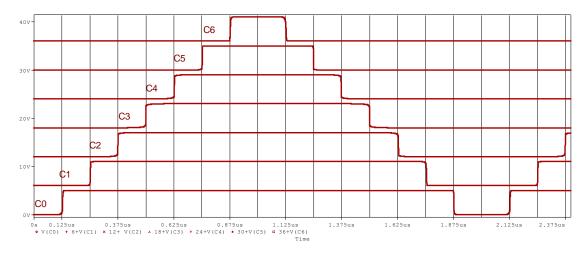

Le signal d'entrée est triangulaire d'amplitude 5 V, de fréquence 500 kHz. On simule sur 2,4 µs. On visualise tout d'abord le fonctionnement des 7 comparateurs :

article 80

Signal d'entrée Vin, et la sortie des 7 comparateurs (0V; 5 V). (pour une meilleur lisibilité, 6 sorties sont présentées décalées verticalement)

On reconnait très nettement le code thermomètre : pour Vin = 0 V, toutes les sorties sont à 0. Puis quand Vin augmente, les sorties passent à 1 progressivement (niveau 5 V). Les changements d'état se font aux seuils prédéterminés (0,625 V, 1,25 V,... 4,375 V). Ces comparateurs étant parfaits, leur commutation se fait quasi instantanément.

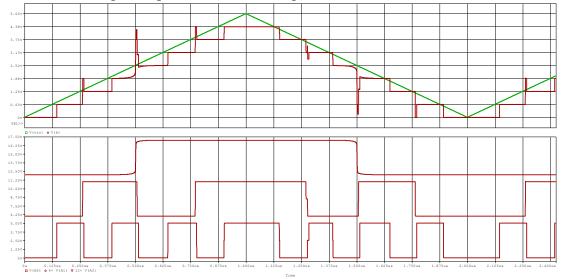

On vérifie également le fonctionnement des transcodeurs :

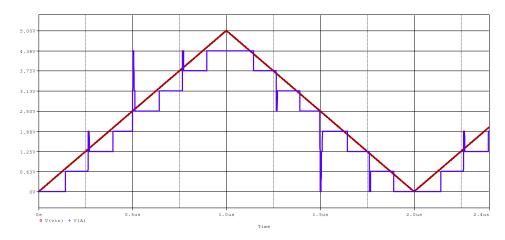

Tension d'entrée Vin, code de Gray, et code binaire naturel. fichier ADC\_3b.cir

- On reconnait le **code de Gray** (un changement d'état ne se fait que sur UNE sortie en même temps). On voit l'influence des temps de traversée des opérateurs logiques de la famille 74AC, par le décalage entre les commutations des comparateurs et celles de G1, G0. Rappelons que C3 = G0 par un fil de liaison.

- On identifie également très bien le code **binaire naturel**. On a clairement un décalage temporel (visible en s'aidant des graduations placées toutes les 125 ns, ce qui correspond au passage des multiples de 1 q = 625 mV de Vin) sur A1, et plus encore sur A0 que la lecture du schéma explique. Quant à A2, c'est le même fil que G2 et C3 : la transition est exactement lors du passage à 2,5 V en Vin.

On remarque donc la conséquence des différents temps de propagation dans les circuits logiques : les sorties binaires s'établissent de facon asynchrone. Il faut un délai suffisant au décodeur pour fournir des valeurs stables sur les 3 sorties.

En zoomant, on mesure 23 ns pour que la valeur numérique soit stabilisée à la valeur exacte : c'est le temps de conversion. Ici, c'est le temps de traversée des 5 couches d'opérateurs logiques de la famille 74AC (environ 3 ns pour l'inverseur et environ 5 ns pour les autres opérateurs).

Cette observation est plus aisée à faire en affichant la sortie du CNA artificiel qui a été ajouté

En ordonnée, les graduations sont tous les 625 mV pour lire facilement les tensions.

article 80

Le signal d'entrée Vin, 500 kHz, triangulaire allant de 0 V à 5 V. Le signal logique [A2 A1 A0] reconstruit après la conversion N/A parfaite.

Sur les transitions qui font transiter plus de 2 bits, on visualise ainsi très bien des valeurs intermédiaires durant l'installation d'une valeur stable. En effet, comme les commutations des sorties A0, A1, A2 sont étalées dans le temps, cela se répercute sur l'affichage de  $V(A) = A2 \times 0.5 + A1 \times 0.25 + A0 \times 0.125$ . Cela donne une indication, pas une mesure.

Rappelons que l'ADC n'est pas commandé par une horloge. C'est parce que le signal d'entrée est une rampe que les changements de valeurs numériques apparaissent régulièrement : avec 5 V (et donc 8 états binaires) parcourus en 1 µs, cela donne 125 ns par état binaire.

#### 2 remarques:

- le temps de conversion serait plus long si les comparateurs avaient leur défaut (temps de propagation, slew rate).

- il faut donc accéder à cette donnée numérique après le temps de conversion. Le circuit logique qui est connecté à ce convertisseur A/N peut être un registre de mémorisation, cadencé par une horloge, dont le front actif sera calé en conséquence.

## 3) Evolution du schéma simulé

Nous avons simulé un ADC flash 3 bits, en statique, en dynamique. Le modèle simplifié des comparateurs a permis d'avoir un temps de conversion de 23 ns, lié essentiellement au temps de réponse des opérateurs logiques de la famille 74AC.

Pour être plus réaliste, nous allons remplacer les sources de tension commandées, par un schéma à transistors. Usuellement, les schémas électroniques de comparateurs s'inspirent des schémas d'amplificateurs opérationnels : étage d'entrée formé de 2 transistors montés en amplificateur différentiel, suivi par une amplification en tension puis un étage de sortie.

La version d'évaluation de Pspice, limitée à 20 transistors, ne peut pas simuler 7 comparateurs + la logique formant les codeurs.

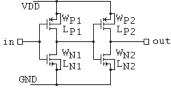

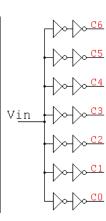

Mais on peut exploiter le fonctionnement d'un **inverseur** logique pour réaliser un comparateur.

#### 3.a) Schéma du comparateur tout ou rien à transistors

L'annexe 4 montre comment 2 inverseurs CMOS peuvent assurer la fonction de comparaison tout ou rien vis à vis d'un seuil de tension VS: par un choix judicieux des W/L des transistors, on peut faire varier la tension de basculement.

Schéma réel : le seuil VS est réglé selon les dimensions W/L

Le sous circuit « comparateurs » qui exploite 8 entrées (Vin et 7 références) et 7 sorties (C0 à C6) est remplacé par 7 sous-circuits, chacun étant à base de 2 inverseurs taillés différemment.

#### 3.b) Simulation des 7 comparateurs. (netlist en annexe 4) fichier TIQ.cir

Le circuit de comparaison nécessite donc  $7 \times 4 = 28$  transistors, ce qui n'est pas simulable avec PSpice version eval. Néanmoins, on peut tout tester en 2 simulations :

- 1) une simulation en validant les lignes X0, X1, X2 et en commentant les lignes X3, X4, X5, X6. Puis, sous Probe, on sauvegarde les potentiels V(C0), V(C1), V(C2) par le menu File...Export Probe Data, dans un fichier avec extension .dat (par exemple C0C1C2.dat).

- 2) une simulation en commentant les lignes X0, X1, X2 et en validant les lignes X3, X4, X5, X6. Il suffit ensuite, sous Probe, menu File... Append Waweform, et chercher le fichier C0C1C2.dat.

De cette façon, tous les potentiels sont disponibles. La figure ci-dessous reprend l'essai réalisé (même signal d'entrée triangulaire en Vin), pour relever le code thermomètre.

La sortie des 7 comparateurs (0V; 5 V). (pour une meilleure lisibilité, 6 sorties sont présentées décalées verticalement)

Le transcodeur n'est pas connecté. Les commutations, moins franches que celles obtenues précédemment en 2.e, doivent coïncider avec les graduations. Or, avec le dimensionnement des transistors utilisés :

- la sortie C3 est la plus rapide (le schéma interne des 2 inverseurs réalisant cette sortie l'explique) : son temps de traversée est inférieur à 1 ns.

- les sorties C0 et C6 sont plus lentes : leur montée présente un retard d'environ 4 ns, leur descente 3 ns.

En première conclusion, il faudrait donc laisser passer un délai d'environ **5 ns** pour lire les données dans leur état stabilisé. Ces bonnes performances sont liées aux valeurs des paramètres placées dans le modèle des transistors.

## 3.c) Simulation des 7 comparateurs + transcodeur. (netlist en annexe 5) fichier ADC\_transcod.cir

Pour avoir les sorties A2, A1, A0, il faut ajouter le transcodeur. Dans ce cas, il faut simuler **tout** le circuit. La version d'évaluation de Pspice ne le permet pas. (En toute rigueur c'est réalisable par des simulations multiples et divers enregistrements, mais c'est fastidieux...)

article 80

Les courbes montrées ci-après exploitent la version Pspice 17.2 « non bridée ».

Trace du haut : Vin et sa conversion en numérique, mais reconstruit en analogique. Trace du bas : la sortie numérique [A2, A1, A0] (présentées décalées verticalement)

On retrouve l'étalement des commutations des sorties A0, A1, A2.

- Le pire cas est la conversion qui arrive ou quitte l'état [111], où le délai est très proche de 28 ns. La raison est le retard apporté par C6 (4 ns déjà mesuré), qu'on ajoute à celui du transcodeur à base d'opérateurs logiques de la famille 74 AC (23 ns déjà mesuré).

Les autres transitions nécessitent environ 25 ns.

- L'affichage de V(A) montre de façon très visuelle les transitions qui mettent en œuvre 2 bits.

Au bilan, la simulation avec cette entrée triangulaire à 500 kHz montre que si on laisse un temps de **28 ns**, la valeur convertie est stable. Mais si les commutations sont plus étalées dans le temps, ce qui arrive avec une entrée qui évolue plus lentement, il est nécessaire de laisser davantage.

#### **Conclusion**

Nous avons simulé dans un premier temps l'ADC flash en exploitant un modèle simplifié des comparateurs. Cette version « allégée » a permis d'exploiter Pspice « lite » ou « étudiante ».

Puis, pour se rapprocher d'un cas plus réel, nous avons fait évoluer notre montage vers un circuit transistorisé. Toujours pour exploiter la version d'évaluation de Pspice, nous avons choisi un schéma très simple des comparateurs : des inverseurs CMOS. Les paramètres de ces transistors ont été choisis pour disposer de fonctions de transfert satisfaisantes. Ce n'est donc pas un schéma fabricable, mais plutôt un schéma de principe. Néanmoins, les mesures de temps de conversion restent cohérentes.

En général, on place en amont d'un convertisseur analogique / numérique, un échantillonneur bloqueur : cela permet de prélever la tension à intervalle régulier, de la bloquer (maintenir sa valeur analogique) durant la conversion. De plus, il faut communiquer la valeur convertie en binaire par le biais d'un registre de mémorisation. Ces 3 éléments : échantillonneur, CAN, mémoire, forment ainsi une chaine d'acquisition.

Dans l'article suivant (n°81 « <u>une chaine d'acquisition avec un ADC flash</u> »), on montre les simulations correspondantes

## Annexe 1 : tableaux de Karnaugh pour obtenir les équations de G1, G0, A1, A0 :

| TK de G | <mark>1</mark> : | On déduit : | G1 = C1C5 |

|---------|------------------|-------------|-----------|

|          |     |      |      |      |      |      |      |      | C3 C2 | C1 C0 |      |      |      |      |      |      |      |

|----------|-----|------|------|------|------|------|------|------|-------|-------|------|------|------|------|------|------|------|

|          |     | 0000 | 0001 | 0011 | 0010 | 0110 | 0111 | 0101 | 0100  | 1100  | 1101 | 1111 | 1110 | 1010 | 1011 | 1001 | 1000 |

| C6 C5 C4 | 000 | 0    | 0    | 1    |      |      | 1    |      |       |       |      | 1    |      |      |      |      |      |

|          | 001 |      |      |      |      |      |      |      |       |       |      | 1    |      |      |      |      |      |

|          | 011 |      |      |      |      |      |      |      |       |       |      | 0    |      |      |      |      |      |

|          | 010 |      |      |      |      |      |      |      |       |       |      |      |      |      |      |      |      |

|          | 110 |      |      |      |      |      |      |      |       |       |      |      |      |      |      |      |      |

|          | 111 |      |      |      |      |      |      |      |       |       |      | 0    |      |      |      |      |      |

|          | 101 |      |      |      |      |      |      |      |       |       |      |      |      |      |      |      |      |

|          | 100 |      |      |      |      |      |      |      |       |       |      |      |      |      |      |      |      |

TK de G0: On déduit :  $G0 = C0 \overline{C2} + C4 \overline{C6}$

|          |     |      |      |      |      |      |      |      | C3 C2 | C1 C0 |      |      |     |      |      |      |      |

|----------|-----|------|------|------|------|------|------|------|-------|-------|------|------|-----|------|------|------|------|

|          |     | 0000 | 0001 | 0011 | 0010 | 0110 | 0111 | 0101 | 0100  | 1100  | 1101 | 1111 | 111 | 1010 | 1011 | 1001 | 1000 |

| C6 C5 C4 | 000 | 0    | 1    | 1    |      |      | 0    |      |       |       |      | 0    |     |      |      |      |      |

|          | 001 |      |      |      |      |      |      |      |       |       |      | - 1  |     |      |      |      |      |

|          | 011 |      |      |      |      |      |      |      |       |       |      | 1    |     |      |      |      |      |

|          | 010 |      |      |      |      |      |      |      |       |       |      |      |     |      |      |      |      |

|          | 110 |      |      |      |      |      |      |      |       |       |      |      |     |      |      |      |      |

|          | 111 |      |      |      |      |      |      |      |       |       |      | 0    |     |      |      |      |      |

|          | 101 |      |      |      |      |      |      |      |       |       |      |      |     |      |      |      |      |

|          | 100 |      |      |      |      |      |      |      |       |       |      |      |     |      |      |      |      |

| TK d | e Al : | On dédu | ait : | A1 = | G2 X0 | OR G1 |

|------|--------|---------|-------|------|-------|-------|

|      |        |         |       | G1   | G0    |       |

|      |        |         | 00    | 01   | 11    | 10    |

|      | G2     | 0       | 0     | 0    | 1     | 1     |

|      |        | 1       | 1     | 1    | 0     | 0     |

| TK d | e A0 : | Oı | n dédu | ıit : | A0 = 0 | 32 XO | R G1 X | KOR G0 |

|------|--------|----|--------|-------|--------|-------|--------|--------|

|      |        |    |        |       | G1     | G0    |        |        |

|      |        |    |        | 00    | 01     | 11    | 10     |        |

|      | G2     |    | 0      | 0     | 1      | 0     | 1      |        |

|      |        |    | 1      | - 1   | 0      | - 1   | 0      |        |

# Annexe 2 : Netlist, ADC flash 3 bits, *prête à simuler*

```

Netlist, ADC flash 3 bits, prête à simuler

convertisseur CNA flash 3 bits

* fichier ADC 3b.cir

.lib dig_io.lib

.lib 74AC.lib

*signaux

Vref ref 0 dc 5V

Vin vin 0 pwl (0,0 1u,5V 2u,0V 3u,5V) DC 2.5V

.DC Vin 0 \bar{5} 1m ; pour carac de transfert

.TRAN .1n 2.4u 0 .1n ; pour test

X1 vin ref C6 C5 C4 C3 C2 C1 C0 CONV

X2 C6 C5 C4 C3 C2 C1 C0 G2 G1 G0 GRAY

X3 G2 G1 G0 A2 A1 A0 BIN

E_NA A 0 POLY(3) (A2,0) (A1,0) (A0,0) 0 0.5 0.25 0.125

.SUBCKT CONV Vin ref C6 C5 C4 C3 C2 C1 C0

R1 ref va 10k

R2 va vb 10k

R3 vb vc 10k

R4 vc vd 10k

R5 vd ve 10k

R6 ve vf 10k

R7 vf vg 10k

R8 vg 0 10k

X0 vin vg C0 COMP

X1 vin vf C1 COMP

X2 vin ve C2 COMP

X3 vin vd C3 COMP

X4 vin vc C4 COMP

X5 vin vb C5 COMP

X6 vin va C6 COMP

.ENDS

.SUBCKT COMP Vp Vm Vs ; in+, in-, out

Ec Vs 0 table {500*(V(Vp)-V(Vm))} (0 0 5 5)

.ENDS

```

#### Annexe 3 : les comparateurs réalisés avec des inverseurs CMOS

### Rappel sur la tension de seuil de basculement d'un inverseur CMOS.

K<sub>N</sub>, K<sub>P</sub>: gains des transistors canal N, P respectivement,

W<sub>N</sub>, L<sub>N</sub> et W<sub>P</sub>, L<sub>P</sub>: largeurs longueurs des transistors canal N, P respectivement.

On pose un coefficient

$$\alpha = \sqrt{\frac{K_{_{N}}}{K_{_{P}}} \frac{W_{_{N}}}{W_{_{P}}} \frac{L_{_{P}}}{L_{_{N}}}}$$

Le **seuil** de basculement d'un inverseur CMOS peut s'écrire : VS =  $\frac{VDD + \alpha V_{TN} - |V_{TP}|}{1 + \alpha}$ . [1]

### Remarques:

- Cette équation montre que  $V_{TN} < VS < VDD$   $|V_{TP}|$ , pour  $\alpha$  allant de l'infini à 0 respectivement.

- Pour une meilleure immunité aux bruits, on cherche à fabriquer des inverseurs à VS = VDD/2.

- $K_N$ ,  $K_P$  sont imposés par la technologie. Le réglage de VS peut être obtenu par un choix judicieux des dimensions (W/L de chaque transistor) pour contre-balancer le fait que  $K_P$  soit différent de  $K_N$ . Si les  $V_T$  des transistors P et N sont identiques en valeur absolue, une valeur de  $\alpha=1$  permet ce résultat. Néanmoins, il est fréquent de s'éloigner quelque peu de cette démarche, car il faut également tenir compte du comportement dynamique de l'inverseur : les mobilités des transistors P et N étant différentes, on a alors  $t_{PLH}$  différent de  $t_{PLH}$ . On peut donc améliorer l'aspect dynamique au détriment de l'aspect statique.

Pour nos comparateurs, on peut utiliser un inverseur CMOS, et par réglage de la taille des transistors, modifier le seuil de basculement. Industriellement, le point délicat de cette méthode est la difficulté d'obtenir une large dynamique de tension de seuil. De plus, une dispersion des caractéristiques des transistors (liée à la fabrication) rend difficile une répétabilité des valeurs des seuils, à géométrie donnée.

Dans notre cas, l'objectif est de remplacer les modèles à base de sources E de Pspice par un schéma, simple à simuler. Le but de cette étude n'est donc pas de lancer une fabrication sur une technologie donnée...

On se permettra de placer des valeurs numériques aux paramètres des transistors, **sans considérations industrielles**, pour réaliser nos 7 comparateurs tout ou rien, tels que les 7 valeurs de VS soient : 0,625 V; 1,25 V; 1,875 V; 2,5 V; 3,125 V; 3,75 V; 4,375 V.

Par [1], il vient alors ces valeurs théoriques, en fixant arbitrairement  $W_P = L_P = 1 \mu$ . On agit sur  $W_N$ ,  $L_N$ .

|             | C0    | C1   | C2  | C3  | C4   | C5    | C6     |

|-------------|-------|------|-----|-----|------|-------|--------|

| $W_N / L_N$ | 310   | 15,5 | 3   | 1   | 0,29 | 0,065 | 0,003  |

| α =         | 17,6  | 3,94 | 4   | 1   | 0,54 | 0,255 | 0,0547 |

| VS =        | 0,626 | 1,25 | 1,8 | 2,5 | 3,13 | 3,75  | 4,38   |

#### Remarque:

Un rapport W/L > 1 est réalisé par W > 1  $\mu$  et L = 1  $\mu$ , et W/L < 1 est réalisé par W = 1  $\mu$  et L > 1  $\mu$ .

Pour améliorer la caractéristique de transfert statique, on place un deuxième inverseur en cascade, ce qui permet également de retrouver le signe. On peut également ajuster les dimensions de ce deuxième inverseur.

article 80

Les inverseurs sont regroupés par 2 pour former un comparateur.

Chaque couple d'inverseurs a ses propres transistors dimensionnés en W et L, afin de disposer de seuil de basculement différent.

Les dimensions de ces 28 transistors sont données dans le tableau ci-dessous.

Il en vient la netliste donnée plus bas, qui permet de simuler ces 7 comparateurs, avec la version d'eval de Pspice.

On fixe une dimension minimale de 1  $\mu$ . Après plusieurs essais qui débutent par les valeurs déterminées par la théorie rappelée en annexe 3, on arrive aux dimensions optimums suivantes :

| Seuil théorique |           | 0,625 V | 1,25 V | 1,875 V | 2,5 V | 3,125 V | 3,75 V | 4,375 V |

|-----------------|-----------|---------|--------|---------|-------|---------|--------|---------|

| Inverseur       | $W/L_P =$ | 1/1     | 1/1    | 1/1     | 1/1   | 1/1     | 1/1    | 1/1     |

| 1               | $W/L_N =$ | 270/1   | 16/1   | 7/2     | 1/1   | 2/7     | 1/16   | 1/270   |

| Inverseur       | $W/L_P =$ | 1/1     | 1/1    | 1/1     | 1/1   | 1/1     | 1/1    | 1/1     |

| 2               | $W/L_N =$ | 2/1     | 16/1   | 3/1     | 1/1   | 1/3     | 1/16   | 1/2     |

```

.SUBCKT COMP 1875 ent sor vdd

test des comparateurs à base d'inverseurs CMOS

* fichier TIQ.cir

Mp1 i ent vdd vdd MODPC W=1u L=1u

Mn1 i ent 0 0 MODNC W=7u L=2u

*signaux

Mp2 sor i vdd vdd MODPC W=1u L=1u

Vdd vdd 0 dc 5V

Mn2 sor i 0 0 MODNC W=3u L=1u

Vin vin 0 pwl (0,0 1u,5V 2u,0V 3u,5V)

. ENDS

.TRAN .1n 2.4u 0 .1n ;

.SUBCKT COMP 25 ent sor vdd

Mp1 i ent vdd vdd MODPC W=1u L=1u

Mn1 i ent 0 0 MODNC W=1u L=1u

* circuit

Mp2 sor i vdd vdd MODPC W=1u L=1u

X0 vin C0 vdd COMP 0625

Mn2 sor i 0 0 MODNC W=1u L=1u

X1 vin C1 vdd COMP 125

X2 vin C2 vdd COMP 1875

.SUBCKT COMP 3125 ent sor vdd

*X3 vin C3 vdd COMP 25

*X4 vin C4 vdd COMP 3125

Mp1 i ent vdd vdd MODPC W=1u L=1u

*X5 vin C5 vdd COMP 375

Mn1 i ent 0 0 MODNC W=2u L=7u

*X6 vin C6 vdd COMP 4375

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=1u L=3u

. ENDS

* transistor maison pour les TIQ

.model MODNC nmos (Level=1 Kp=3m Vto=0.4

.SUBCKT COMP 375 ent sor vdd

+ Cgdo=3.5n Cgso=3.5n lambda=0.002 )

Mp1 i ent vdd vdd MODPC W=1u L=1u

.model MODPC pmos ( Level=1 Kp=3m Vto=-0.4

Mn1 i ent 0 0 MODNC W=1u L=16u

+ Cgdo=3.5n Cgso=3.5n lambda=0.002 )

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=1u L=16u

.SUBCKT COMP 0625 ent sor vdd

.ENDS

Mp1 i ent vdd vdd MODPC W=1u L=1u

Mn1 i ent 0 0 MODNC W=270u L=1u

.SUBCKT COMP 4375 ent sor vdd

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mp1 i ent vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=2u L=1u

Mn1 i ent 0 0 MODNC W=1u L=270u

. ENDS

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=1u L=2u

.SUBCKT COMP_125 ent sor vdd

.ENDS

Mp1 i ent vdd vdd MODPC W=1u L=1u

. PROBE

Mn1 i ent 0 0 MODNC W=16u L=1u

Mp2 sor i vdd vdd MODPC W=1u L=1u

. END

Mn2 sor i 0 0 MODNC W=16u L=1u

prête à simuler

```

#### Annexe 5 : Netlist, ADC flash à inverseurs CMOS + logique de transcodage

article 80

Le schéma complet montre 7 comparateurs à base de transistors CMOS, et la logique de codage à base de portes de la famille 74AC :

La netliste ci-dessous lui correspond.

La version d'évaluation de Pspice ne permet pas de faire cette simulation.

```

CNA flash 3 bits complet

* fichier ADC transcod.cir

.SUBCKT COMP 25 ent sor vdd

* necessite Pspice complet

Mp1 i ent vdd vdd MODPC W=1u L=1u

Mn1 i ent 0 0 MODNC W=1u L=1u

.lib dig_io.lib

Mp2 sor i vdd vdd MODPC W=1u L=1u

.lib 74AC.lib

Mn2 sor i 0 0 MODNC W=1u L=1u

*signaux

Vdd vdd 0 dc 5V

.SUBCKT COMP 3125 ent sor vdd

Mp1 i ent vdd vdd MODPC W=1u L=1u

Vin vin 0 pwl (0,0 1u,5V 2u,0V 3u,5V)

Mn1 i ent 0 0 MODNC W=2u L=7u

.TRAN .1n 2.4u 0 .1n

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=1u L=3u

* circuit :

.ENDS

X1 vin C6 C5 C4 C3 C2 C1 C0 vdd CONV

X2 C6 C5 C4 C3 C2 C1 C0 G2 G1 G0 GRAY

.SUBCKT COMP 375 ent sor vdd

Mp1 i ent vdd vdd MODPC W=1u L=1u

X3 G2 G1 G0 A2 A1 A0 BIN

E NA A 0 POLY(3) (A2,0) (A1,0) (A0,0) 0 0.5 0.25 0.125

Mn1 i ent 0 0 MODNC W=1u L=16u

Mp2 sor i vdd vdd MODPC W=1u L=1u

.SUBCKT CONV Vin C6 C5 C4 C3 C2 C1 C0 vdd

Mn2 sor i 0 0 MODNC W=1u L=16u

X0 vin C0 vdd COMP 0625

.ENDS

X1 vin C1 vdd COMP_125

X2 vin C2 vdd COMP 1875

.SUBCKT COMP 4375 ent sor vdd

X3 vin C3 vdd COMP 25

Mp1 i ent vdd vdd MODPC W=1u L=1u

X4 vin C4 vdd COMP_3125

Mn1 i ent 0 0 MODNC W=1u L=270u

X5 vin C5 vdd COMP 375

Mp2 sor i vdd vdd MODPC W=1u L=1u

X6 vin C6 vdd COMP 4375

Mn2 sor i 0 0 MODNC W=1u L=2u

. ENDS

* transistor maison pour les TIQ

.SUBCKT GRAY C6 C5 C4 C3 C2 C1 C0 G2 G1 G0

.model MODNC nmos ( Level=1 Kp=3m Vto=0.4

Rshunt C3 G2 1

X_inv_1 C6 C6b $G_DPWR $G_DGND 74AC04

+ Cgdo=3.5n Cgso=3.5n lambda=0.002 )

.model MODPC pmos ( Level=1 Kp=3m Vto=-0.4

X inv 2 C2 C2b $G DPWR $G DGND 74AC04

+ Cgdo=3.5n Cgso=3.5n lambda=0.002 )

X inv 3 C5 C5b $G DPWR $G DGND 74AC04

X_AND2_1 C1 C5b G1 $G_DPWR $G_DGND 74AC08

.SUBCKT COMP 0625 ent sor vdd

X AND2 2 CO C2b S1 $G DPWR $G DGND 74AC08

Mp1 i ent vdd vdd MODPC W=1u L=1u

X AND2 3 C4 C6b S2 $G DPWR $G DGND 74AC08

Mn1 i ent 0 0 MODNC W=270u L=1u

X_OR2 S1 S2 G0 $G_DPWR $G_DGND 74AC32

Mp2 sor i vdd vdd MODPC W=1u L=1u

RG2 G2 0 100k

Mn2 sor i 0 0 MODNC W=2u L=1u

RG1 G1 0 100k

RG0 G0 0 100k

ENDS

ENDS

.SUBCKT COMP 125 ent sor vdd

Mp1 i ent vdd vdd MODPC W=1u L=1u

.SUBCKT BIN G2 G1 G0 A2 A1 A0

Mn1 i ent 0 0 MODNC W=16u L=1u

Rshunt G2 A2 1

X XOR 1 G2 G1 A1 $G DPWR $G DGND 74AC86

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=16u L=1u

X XOR 2 A1 G0 A0 $G DPWR $G DGND 74AC86

RA2 A2 0 100k

.ENDS

RA1 A1 0 100k

.SUBCKT COMP_1875 ent sor vdd

RAO AO O 100k

Mp1 i ent vdd vdd MODPC W=1u L=1u

. ENDS

Mn1 i ent 0 0 MODNC W=7u L=2u

. PROBE

Mp2 sor i vdd vdd MODPC W=1u L=1u

Mn2 sor i 0 0 MODNC W=3u L=1u

. END

```

## articles 1 à 43 : sur le livre

| Tableau récapitulatif des articles PDF disponibles sur ce site |                                                              |                     |                     |  |  |  |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------|---------------------|---------------------|--|--|--|--|--|--|--|

| n°                                                             | titre                                                        | lien présentation   | lien direct article |  |  |  |  |  |  |  |

|                                                                | Guide d'installation et d'emploi simplifié                   | présentation        | document PDF        |  |  |  |  |  |  |  |

| 44                                                             | Exemples basiques et des exercices                           | présentation        | document PDF        |  |  |  |  |  |  |  |

| 45                                                             | Un exemple de circuit passif                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 46                                                             | Un oscillateur Colpitts                                      | présentation        | document PDF        |  |  |  |  |  |  |  |

| 47                                                             | Compensation en fréquence des amplificateurs opérationnels   | présentation        | document PDF        |  |  |  |  |  |  |  |

| 48                                                             | Un amplificateur à transistors bipolaires                    | présentation        | document PDF        |  |  |  |  |  |  |  |

| 49                                                             | Une bascule D Flip Flop CMOS                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 50                                                             | Une porte XOR à transistors MOS                              | présentation        | document PDF        |  |  |  |  |  |  |  |

| 51                                                             | Un VCO à 12 transistors MOS                                  | présentation        | document PDF        |  |  |  |  |  |  |  |

| 52                                                             | Une PLL à moins de 20 transistors MOS                        | présentation        | document PDF        |  |  |  |  |  |  |  |

| 53                                                             | Un oscillateur à résistance négative                         | présentation        | document PDF        |  |  |  |  |  |  |  |

| 54                                                             | Une charge électronique                                      | présentation        | document PDF        |  |  |  |  |  |  |  |

| 55                                                             | Un amplificateur en classe C                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 56                                                             | Le monostable 74 123                                         | présentation        | document PDF        |  |  |  |  |  |  |  |

| 57                                                             | Un amplificateur en classe D                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 58                                                             | Le transformateur en linéaire                                | présentation        | document PDF        |  |  |  |  |  |  |  |

| 59                                                             | La loi d'ohm thermique                                       | présentation        | document PDF        |  |  |  |  |  |  |  |

| 60                                                             | Le transformateur en non linéaire                            | présentation        | document PDF        |  |  |  |  |  |  |  |

| 61                                                             | Robustesse d'un oscillateur en anneau                        | présentation        | document PDF        |  |  |  |  |  |  |  |

| 62                                                             | Une alimentation stabilisée                                  | présentation        | document PDF        |  |  |  |  |  |  |  |

| 63                                                             | Modélisation d'un haut-parleur                               | présentation        | document PDF        |  |  |  |  |  |  |  |

| 64                                                             | Un synthétiseur de fréquence                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 65                                                             | Un ampli audio de Sparkfun                                   | présentation        | document PDF        |  |  |  |  |  |  |  |

| 66                                                             | Simulation logique et analogique                             | présentation        | document PDF        |  |  |  |  |  |  |  |

| 67                                                             | Un oscillateur à relaxation                                  | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 68                                                             | Lecteur de TAG RFID 125 kHz                                  | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 69                                                             | Diagramme de l'œil avec Pspice                               | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 70                                                             | Un amplificateur hautes fréquences                           | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 71                                                             | Une bizarrerie enfin expliquée                               | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 72                                                             | Comprendre le paramétrage de la FFT                          | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 73                                                             | La relation de Bennett                                       | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 74                                                             | Simuler un circuit à plus de 20 transistors avec PSpice Eval | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 75                                                             | Une horloge biphase sans recouvrement                        | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 76                                                             | Quelques simulations sur la diode                            | présentation        | document PDF        |  |  |  |  |  |  |  |

| 77                                                             | Un ampli classe A, avec transformateur de sortie             | présentation        | document PDF        |  |  |  |  |  |  |  |

| 78                                                             | Des stimuli pour PSpice                                      | présentation        | document PDF        |  |  |  |  |  |  |  |

| 79                                                             | Simuler le TL431 : zener ajustable                           | présentation        | document PDF        |  |  |  |  |  |  |  |

| 80                                                             | Un ADC flash                                                 | présentation        | document PDF        |  |  |  |  |  |  |  |

| 81                                                             | Une chaine d'acquisition : S&H, ADC, DAC                     | présentation        | document PDF        |  |  |  |  |  |  |  |

| 82                                                             | Un amplificateur 50 MHz                                      | présentation        | document PDF        |  |  |  |  |  |  |  |

| 83                                                             | Un dérivateur non inverseur                                  | présentation        | document PDF        |  |  |  |  |  |  |  |

| 84                                                             | Un amplificateur bipolaire avec push pull CMOS               | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 85                                                             | Rôle des répéteurs logiques dans un circuit intégré          | présentation        | document PDF        |  |  |  |  |  |  |  |

| 86                                                             | Un driver logique CMOS pour charge 50 ohms                   | présentation        | document PDF        |  |  |  |  |  |  |  |

| 87                                                             | Des triggers de Schmitt et des applications                  | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| 88                                                             | Un filtre gaussien analogique                                | présentation        | document PDF        |  |  |  |  |  |  |  |

| 89                                                             | Un générateur de bruit rose                                  | <u>présentation</u> | document PDF        |  |  |  |  |  |  |  |

| Com                       | prendre l'électronique par la simulation, par S. Dusausay article 80                              | pages suppléme      | ntaires 2024/2025 |  |  |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------|---------------------|-------------------|--|--|--|--|--|--|--|

| 90                        | Un anémomètre à fil chaud : simulation comportementale                                            | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 91                        | Un oscillateur à pont de Wien stabilisé par CTN                                                   | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 92                        | L'emballement thermique d'une diode                                                               | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 93                        | Les puissances dans un amplificateur                                                              | présentation        | document PDF      |  |  |  |  |  |  |  |

| 94                        | Asservissement de puissance dans une résistance                                                   | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 95                        | Asservissement de la puissance émise par une antenne radio                                        | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 96                        | Un driver de LED de puissance                                                                     | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 97                        | Exploiter Pspice pour simuler des filtres numériques                                              | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 98                        | Un filtre en cosinus surélevé avec Pspice                                                         | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 99                        | Effet de la température sur un amplificateur en classe A                                          | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

| 100                       | Un amplificateur à transistors JFET et bipolaires                                                 | <u>présentation</u> | document PDF      |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

| Supplément, hors article: |                                                                                                   |                     |                   |  |  |  |  |  |  |  |

|                           | mon cours « Electronique pour les communications numériques ». polycopié couleur 201 pages en pdf |                     |                   |  |  |  |  |  |  |  |

retour à l'écran d'accueil de ce site